## 15867339858

### BCM84891L

# 10GBASE-T/5GBASE-T/2.5GBASE-T/1000BASE-T/100BASE-TX Transceiver

### **General Description**

The Broadcom® BCM84891L is a single 10GBASE-T/5GBASE-T/2.5GBASE-T/1000BASE-T/100BASE-TX Ethernet CMOS transceiver. The device performs all physical-layer functions for 10GBASE-T, 5GBASE-T, 2.5GBASE-T, 1000BASE-T, and 100BASE-TX Ethernet on Category 6, 6A, or 7 twisted-pair cable. The 5GBASE-T, 2.5GBASE-T, 1000BASE-T, and 100BASE-TX can operate on standard Category 5e UTP. The BCM84891L supports the XFI/10GBASE-KR, USXGMII, 5000BASE-R, 2500BASE-R, 5000BASE-X, 2500BASE-X, and 1000BASE-X (SGMII) interface for connection to a MAC. The BCM84891L is a highly integrated solution that combines digital adaptive equalizers, ADCs, phase-locked loops, line drivers, encoders, decoders, echo cancelers, crosstalk cancelers, and all the required support circuitry.

The BCM84891L features the Energy Efficient Ethernet (EEE) protocol. EEE enables the BCM84891L to autonegotiate and operate with EEE-compliant link partners to reduce overall system power during low utilization of the link. Broadcom's AutogrEEEn® mode permits legacy systems to enjoy the power saving benefits of EEE.

The BCM84891L automatically negotiates an operating speed with any transceiver on the opposite end of the line. The BCM84891L features Enhanced Cable Diagnostics, which detects common cable problems such as shorts, opens, and cable length.

## **Applications**

- 10-Gigabit Ethernet (GbE) switches and uplinks

- 10GbE server adapter

- 10GbE host control

#### **Features**

- Single-chip integrated single Ethernet transceiver-MAC to magnetics:

- 10GBASE-T IEEE 802.3an

- 5GBASE-T IEEE 802.3bz

- 2.5GBASE-T IEEE 802.3bz

- 1000BASE-T IEEE 802.3ab

- 100BASE-TX IEEE 802.3u

- IEEE 802.3z

- IEEE 802.3az

- XFI/10GBASE-KR, USXGMII, 5000BASE-X, 2500BASE-X, 5000BASE-R, 2500BASE-R, and 1000BASE-X (SGMII) MAC Interface

- 5G rate over USXGMII/XFI/5000BASE-R/5000BASE-X MAC interface

- 2.5G rate over USXGMII/XFI/2500BASE-R/2500BASE-X MAC interface

- IEEE 1588-2008 version 2-compliant

- IEEE fast retrain and link monitoring

- EEE on 10GBASE-T, 5GBASE-T, 2.5GBASE-T, 1000BASE-T, and 100BASE-TX Auto-sense mode

- Trace matched output impedance

- Line-side loopback

- Low electromagnetic interference (EMI) emissions

- Enhanced cable diagnostics

- Support for jumbo packets up to 18 KB

- Detection and correction of pair swaps (MDI crossover), pair skew, and pair polarity

- Auto-negotiation with next page support

- IEEE 1149.1 (JTAG) and IEEE 1149.6 (ACJTAG) boundary scan support

- Low-power, 0.8V CMOS core

- 1.2V, 2.5V, or 3.3V MDIO I/O, 1.8V CMOS I/O

- Device package: 8 mm × 8 mm BGA

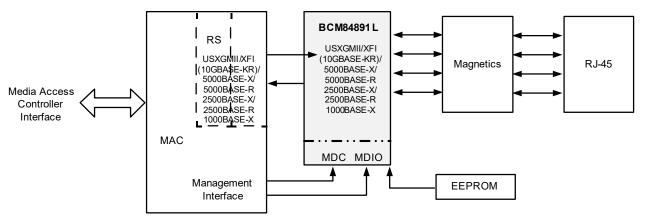

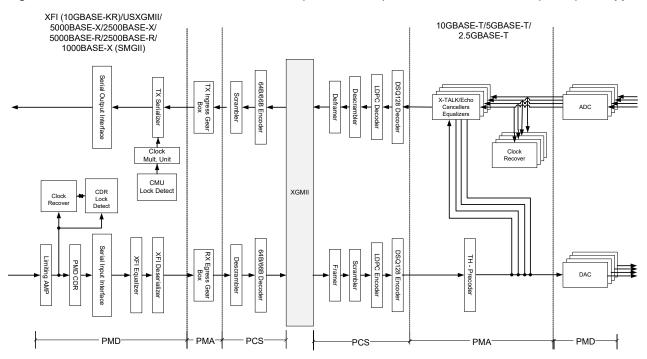

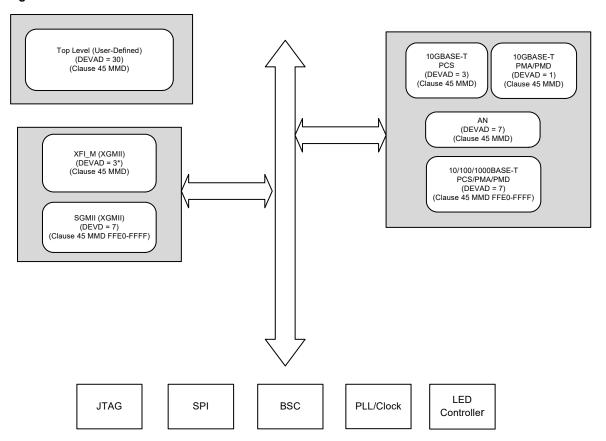

Figure 1: Functional Block Diagram

## 15867339858

## **Table of Contents**

## 15867339858

|       | ter 1: Functional Description                                                |    |

|-------|------------------------------------------------------------------------------|----|

|       | Overview                                                                     |    |

| 1.2 I | Device Functions                                                             | 17 |

| 1.3   | Operation Modes                                                              | 18 |

| 1.4   | 10GBASE-T                                                                    | 18 |

| •     | 1.4.1 Transmit Path                                                          | 18 |

|       | 1.4.1.1 Scramble and Frame                                                   | 18 |

|       | 1.4.1.2 LDPC Encode                                                          | 19 |

|       | 1.4.1.3 DSQ128 Map (10GBASE-T)                                               | 19 |

|       | 1.4.1.4 PAM16 Mapping (IEEE 802.3bz)                                         | 19 |

|       | 1.4.1.5 Tomlinson-Harashima Precode                                          | 19 |

|       | 1.4.1.6 DAC                                                                  | 19 |

|       | 1.4.2 Receive Path                                                           | 19 |

|       | 1.4.2.1 Four-Channel ADC                                                     | 19 |

|       | 1.4.2.2 Clock Recovery                                                       | 20 |

|       | 1.4.2.3 Matrix Crosstalk Canceler and Equalizer                              | 20 |

|       | 1.4.2.4 Echo Canceler                                                        | 20 |

|       | 1.4.2.5 Four-Channel DSQ128 Soft LDP Decision and LDPC Decoder (10GBASE-T)   | 20 |

|       | 1.4.2.6 Four-Channel PAM16 Soft LDP Decision and LDPC Decoder (IEEE 802.3bz) | 20 |

|       | 1.4.2.7 Deframe and Descramble                                               | 21 |

|       | XFI (10GBASE-KR)/USXGMII/5000BASE-X/2500BASE-X/<br>000BASE-R/2500BASE-R      | 21 |

|       | 1.5.1 Transmit Path                                                          | 21 |

|       | 1.5.1.1 64-Bit/66-Bit Encoder                                                | 21 |

|       | 1.5.1.2 XFI (10GBASE-KR) Ingress TX Gearbox                                  | 21 |

|       | 1.5.1.3 XFI (10GBASE-KR) Ingress TX Serializer                               | 21 |

|       | 1.5.1.4 XFI (10GBASE-KR) Clock Multiplication Unit                           | 22 |

|       | 1.5.1.5 XFI (10GBASE-KR) CMU Lock Detect                                     | 22 |

|       | 1.5.1.6 XFI (10GBASE-KR) CMOS Differential Serial Output Interface           | 22 |

|       | 1.5.2 Receive Path                                                           | 23 |

|       | 1.5.2.1 Limiting Amplifier                                                   | 23 |

|       | 1.5.2.2 XFI/10GBASE-KR Clock Recovery                                        | 23 |

|       | 1.5.2.3 XFI/10GBASE-KR CDR Lock Detect                                       |    |

|       | 1.5.2.4 XFI/10GBASE-KR PMD CDR Lock to Incoming Data Detector                |    |

|       | 1.5.2.5 XFI/10GBASE-KR Serial Input Interface                                |    |

|       | 1.5.2.6 XFI/10GBASE-KR Equalizer                                             |    |

|       | 1.5.2.7 XFI/10GBASE-KR Deserializer                                          |    |

|       | 1.5.2.8 XFI/10GBASE-KR Egress RX Gearbox                                     | 24 |

| 1.5.2.9 64-Bit/66-Bit Synchronizer/Decoder                   | 158673398584 |

|--------------------------------------------------------------|--------------|

| 1.6 5G or 2.5G Rate Over XFI Interface in 10GBASE-R          |              |

| 1.7 100BASE-TX/1000BASE-T                                    |              |

| 1.7.1 Encoder                                                |              |

| 1.7.2 Decoder                                                | 26           |

| 1.7.3 Carrier Sense                                          | 26           |

| 1.7.4 Link Monitor                                           | 26           |

| 1.7.5 Digital Adaptive Equalizer (100/1000BASE-T Only)       | 26           |

| 1.7.6 Echo Canceler                                          | 27           |

| 1.7.7 Crosstalk Canceler                                     | 27           |

| 1.7.8 Analog-to-Digital Converter                            | 27           |

| 1.7.9 Clock Recovery/Generator                               | 27           |

| 1.7.10 Baseline Wander Correction                            | 27           |

| 1.7.11 Multimode TX Digital-to-Analog Converter              | 28           |

| 1.7.12 Stream Cipher                                         | 28           |

| 1.7.13 Wire Map and Pair Skew Correction                     | 28           |

| 1.7.14 Automatic MDI Crossover                               | 29           |

| 1.7.15 100BASE-TX Forced Mode Auto-MDIX                      | 29           |

| 1.8 Auto-Negotiation                                         | 29           |

| 1.8.1 Copper Interface                                       | 29           |

| 1.9 5000BASE-X Interface                                     | 30           |

| 1.10 2500BASE-X Interface                                    | 30           |

| 1.11 Serial GMII Interface                                   | 30           |

| 1.12 USXGMII Interface                                       | 30           |

| 1.13 Synchronous Ethernet (SyncE) Recovered Clock            | 30           |

| 1.13.1 SYNC_E Configuration 1 (DEVAD = 30, Address = 0x404F) | )30          |

| 1.13.2 SYNC Common CFG Register (DEVAD = 30, Address = 0x    | A04C)31      |

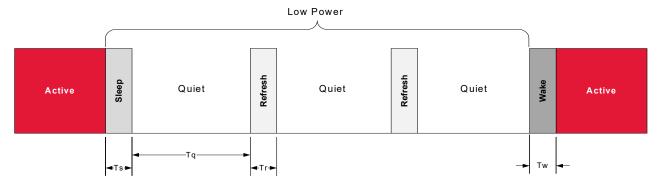

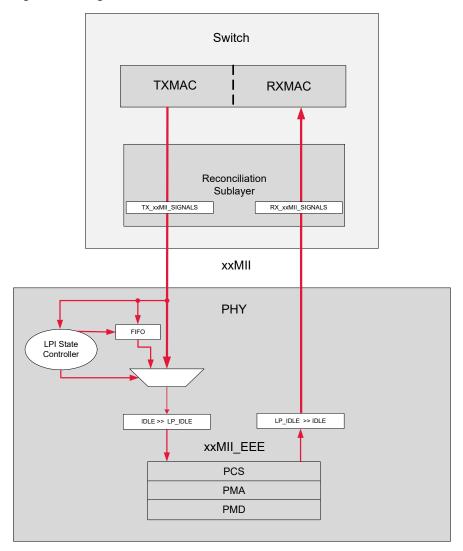

| 1.14 Energy Efficient Ethernet                               | 31           |

| 1.14.1 IEEE EEE Mode                                         | 32           |

| 1.14.1.1 Transmit Direction                                  | 32           |

| 1.14.1.2 Receive Direction                                   | 33           |

| 1.14.2 AutogrEEEn Mode                                       |              |

| 1.14.2.1 Idle Threshold                                      | 35           |

| 1.14.2.2 Constant Latency Operation                          | 35           |

| 1.14.2.3 Variable Latency Operation                          |              |

| 1.15 Enabling and Disabling the EEE Feature in the PHY       |              |

| 1.15.1 Enabling IEEE EEE Mode                                |              |

| 1.15.2 Disabling IEEE EEE Mode                               |              |

| 1.15.3 Enabling AutogrEEEn Mode                              |              |

| 1.15.4 Disabling AutogrEEEn Mode                             | 36           |

| 1.15.5 Monitoring EEE Readiness                                   | 1586/3398587  |

|-------------------------------------------------------------------|---------------|

| 1.15.6 Fast Retrain                                               |               |

| 1.15.6.1 IEEE Fast Retrain Mode                                   | 37            |

| 1.15.6.2 Negotiated Fast Retrain (NFR) Mode                       | 37            |

| 1.15.6.3 BCM84891L-Proprietary Fast Retrain Mode                  | 37            |

| 1.16 Jumbo Packets                                                | 37            |

| 1.17 HiGig2 <sup>™</sup> Messages Support                         | 37            |

| 1.18 Loopback Operation                                           | 38            |

| 1.18.1 XFI/10GBASE-KR System Loopback at PCS/PMA of 10GBASE-T/100 | 0/100BASE-T38 |

| 1.18.1.1 Loopback at PCS of 10GBASE-T                             | 38            |

| 1.18.1.2 Loopback at PCS for 5GBASE-T                             | 38            |

| 1.18.1.3 Loopback at PCS for 2.5GBASE-T                           | 38            |

| 1.18.1.4 Loopback at PCS of 1000/100BASE-T                        | 38            |

| 1.18.1.5 Loopback at PCS of 100BASE-T                             | 38            |

| 1.18.2 Copper (10G) Line Loopback at PMD/PCS of XFI/10GBASE-KR    | 38            |

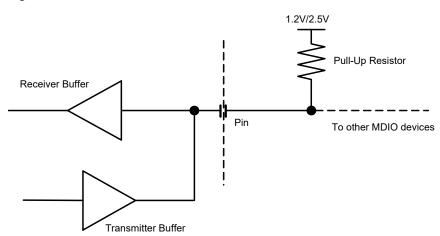

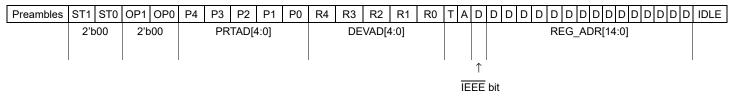

| 1.19 Management Interface                                         | 39            |

| 1.20 TRD (MDI) Interface Pair Swapping                            | 40            |

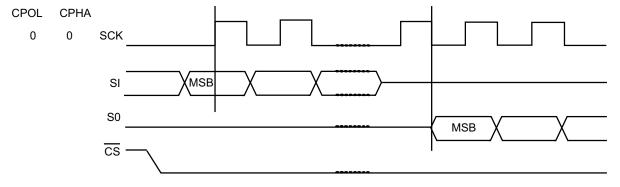

| 1.21 SPI Interface                                                | 40            |

| 1.21.1 SPI Modes                                                  | 40            |

| 1.21.2 Functional Description                                     | 41            |

| 1.21.3 Read Data Bytes (READ)                                     | 41            |

| 1.21.4 SPI Memory Power-Up Sequence                               | 42            |

| 1.22 MDIO Command Handler Function                                | 42            |

| 1.22.1 MDIO Command Handler Theory of Operation                   | 44            |

| 1.22.2 Command Procedure                                          | 44            |

| 1.22.3 Provisioning and Monitoring Sequences                      |               |

| 1.23 Command Descriptions                                         | 47            |

| 1.23.1 Enable/Disable/View Commands                               | 47            |

| 1.23.1.1 CMD_ GET_PAIR_SWAP                                       | 47            |

| 1.23.1.2 CMD_SET_PAIR_SWAP                                        |               |

| 1.23.1.3 Pair Swap Values for Odd Ports                           | 47            |

| 1.23.1.4 Pair Swap Values for Even Ports                          |               |

| 1.23.1.5 CMD_ GET_1588_ENABLE                                     | 48            |

| 1.23.1.6 CMD_SET_1588_ENABLE                                      |               |

| 1.23.1.7 GET_LIMITED_REACH_MODE_ENABLE                            |               |

| 1.23.1.8 SET_LIMITED_REACH_MODE_ENABLE                            |               |

| 1.23.1.9 CMD_GET_EEE_MODE                                         |               |

| 1.23.1.10 CMD_SET_EEE_MODE                                        |               |

| 1.23.1.11 CMD_ GET_EMI_MODE_ENABLE                                |               |

| 1.23.1.12 CMD_SET_EMI_MODE_ENABLE                                 | 52            |

|      |              |                                                            | 1E0472200E0 |

|------|--------------|------------------------------------------------------------|-------------|

|      |              | CMD_GET_SUB_LF_RF_STATUS                                   |             |

|      |              | CMD_CLEAR_SUB_LF_RF                                        |             |

|      |              | CMD_SET_SUB_LF_RF                                          |             |

|      |              | GET_KR_MODE_ENABLE                                         |             |

|      |              | SET_KR_MODE_ENABLE                                         |             |

|      |              | GET_XFI_TX_FILTERS                                         |             |

|      |              | SET_XFI_TX_FILTERS                                         |             |

|      |              | GET_XFI_POLARITY                                           |             |

|      | 1.23.1.21    | SET_XFI_POLARITY                                           | 53          |

|      |              | GET_CURRENT_VOLTAGE                                        |             |

|      |              | CMD_GET_SNR                                                |             |

|      | 1.23.1.24    | CMD_GET_CURRENT_TEMP                                       | 54          |

|      | 1.23.1.25    | CMD_SET_UPPER_TEMP_WARNING_LEVEL                           | 54          |

|      | 1.23.1.26    | CMD_GET_UPPER_TEMP_WARNING_LEVEL                           | 54          |

|      | 1.23.1.27    | CMD_SET_LOWER_TEMP_WARNING_LEVEL                           | 54          |

|      | 1.23.1.28    | CMD_GET_LOWER_TEMP_WARNING_LEVEL                           | 55          |

|      | 1.23.1.29    | READ_INDIRECT_GPHY_REG_BITS                                | 55          |

|      | 1.23.1.30    | WRITE_INDIRECT_GPHY_REG_BITS                               | 56          |

|      | 1.23.1.31    | GET_802.3BZ_PRIORITY                                       | 56          |

|      | 1.23.1.32    | SET_802.3BZ_PRIORITY                                       | 56          |

|      | 1.23.1.33    | GET_XFI_2P5G_5G_MODE                                       | 57          |

|      | 1.23.1.34    | SET_XFI_2P5G_5G_MODE                                       | 57          |

|      | 1.23.1.35    | GET_EEE_STATISTICS                                         | 57          |

|      | 1.23.1.36    | GET_JUMBO_PACKET                                           | 57          |

|      | 1.23.1.37    | SET_JUMBO_PACKET                                           | 58          |

|      | 1.23.1.38    | GET_PAUSE_FRAME_MODE                                       | 58          |

|      | 1.23.1.39    | SET_PAUSE_FRAME_MODE                                       | 58          |

|      | 1.23.1.40    | GET_USXGMII                                                | 58          |

|      |              | SET_USXGMII                                                |             |

| 1.24 | General-Pur  | pose LED Programmability                                   | 59          |

| 1.25 | Power Supp   | lies                                                       | 61          |

| 1.26 | Reset        |                                                            | 61          |

| Chap | ter 2: Regis | ter Summary                                                | 62          |

|      | _            | egisters through MDC/MDIO Management Interfaces            |             |

|      | _            | r Programming                                              |             |

|      | •            | EEE P802.3ae Extension Frame Register Access Clause 45 Moo |             |

| 2.2  |              | s                                                          |             |

|      |              | itions                                                     |             |

|      | •            | Register                                                   |             |

|      |              | SE-T Register Description (DEVAD = 1 PMA)                  |             |

|      |              | - , , , , , , , , , , , , , , , , , , ,                    |             |

| 2.4.1.1 PMA/PMD Control 1 Register (DEVAD = 1, Address = 0x0000)                                 | 5.9/6.0.65 |

|--------------------------------------------------------------------------------------------------|------------|

| 2.4.1.2 PMA/PMD Status 1 Register (DEVAD = 1, Address = 0x0001)                                  |            |

| 2.4.1.3 PMA/PMD Device Identifier Part 0 (DEVAD = 1, Address = 0x0002)                           | 66         |

| 2.4.1.4 PMA/PMD Device Identifier Part 1 (DEVAD = 1, Address = 0x0003)                           | 66         |

| 2.4.1.5 PMA/PMD Speed Ability (DEVAD = 1, Address = 0x0004)                                      | 67         |

| 2.4.1.6 Devices in Package Register Part 0 (DEVAD = 1, Address = 0x0005)                         | 68         |

| 2.4.1.7 Devices in Package Register Part 1 (DEVAD = 1, Address = 0x0006)                         | 68         |

| 2.4.1.8 PMA/PMD Control 2 Register (DEVAD = 1, Address = 0x0007)                                 | 69         |

| 2.4.1.9 10G PMA/PMD Status 2 Register (DEVAD = 1, Address = 0x0008)                              | 69         |

| 2.4.1.10 10G PMA/PMD Transmit Disable (DEVAD = 1, Address = 0x0009)                              | 71         |

| 2.4.1.11 10G PMD Receive Signal Detect (DEVAD = 1, Address = 0x000A)                             | 71         |

| 2.4.1.12 10G PMA/PMD Extended Ability (DEVAD = 1, Address = 0x000B)                              | 72         |

| 2.4.1.13 PMA/PMD Package Identifier (DEVAD = 1, Address = 0x000E)                                | 72         |

| 2.4.1.14 PMA/PMD Package Identifier (DEVAD = 1, Address = 0x000F)                                | 72         |

| 2.4.1.15 10GBASE-T Status (DEVAD = 1, Address = 0x0081)                                          | 73         |

| 2.4.1.16 PMD_IEEE_EXT_AB_2P5G_5G to 2.5G/5G PMA/PMD Extended Ability (DEVAD =1, Address =0x0015) | 73         |

| 2.4.1.17 10GBASE-T Pair Swap and Polarity (DEVAD = 1, Address = 0x0082)                          | 73         |

| 2.4.1.18 10GBASE-T TX Power Backoff and PHY Limited Reach Setting (DEVAD = 1, Address = 0x0083)  | 74         |

| 2.4.1.19 10GBASE-T Test Mode (DEVAD = 1, Address = 0x0084)                                       | 75         |

| 2.4.1.20 10GBASE-T SNR Operating Margin CH A (DEVAD = 1, Address = 0x0085)                       |            |

| 2.4.1.21 10GBASE-T SNR Operating Margin CH B (DEVAD = 1, Address = 0x0086)                       |            |

| 2.4.1.22 10GBASE-T SNR Operating Margin CH C (DEVAD = 1, Address = 0x0087)                       | 76         |

| 2.4.1.23 10GBASE-T SNR Operating Margin CH D (DEVAD = 1, Address = 0x0088)                       | 76         |

| 2.4.1.24 10GBASE-T SNR Minimum Margin CH A (DEVAD = 1, Address = 0x0089)                         |            |

| 2.4.1.25 10GBASE-T SNR Minimum Margin CH B (DEVAD = 1, Address = 0x008A)                         | 76         |

| 2.4.1.26 10GBASE-T SNR Minimum Margin CH C (DEVAD = 1, Address = 0x008B)                         | 77         |

| 2.4.1.27 10GBASE-T SNR Minimum Margin CH D (DEVAD = 1, Address = 0x008C)                         |            |

| 2.4.1.28 10GBASE-T RX Signal Power CH A (DEVAD = 1, Address = 0x008D)                            | 77         |

| 2.4.1.29 10GBASE-T RX Signal Power CH B (DEVAD = 1, Address = 0x008E)                            | 77         |

| 2.4.1.30 10GBASE-T RX Signal Power CH C (DEVAD = 1, Address = 0x008F)                            | 78         |

| 2.4.1.31 10GBASE-T RX Signal Power CH D (DEVAD = 1, Address = 0x0090)                            | 78         |

| 2.4.1.32 10GBASE-T Skew Delay Part 0 (DEVAD = 1, Address = 0x0091)                               | 78         |

| 2.4.1.33 10GBASE-T Skew Delay Part 1 (DEVAD = 1, Address = 0x0092)                               | 79         |

| 2.4.1.34 IEEE Fast Retrain Register (DEVAD = 1, Address = 0x0093)                                | 79         |

| 2.4.1.35 Download Processor Control (DEVAD = 1, Address = 0xA817)                                | 80         |

| 2.4.1.36 Download Status (DEVAD = 1, Address = 0xA818)                                           | 80         |

| 2.4.1.37 Download Address Low (DEVAD = 1, Address = 0xA819)                                      | 80         |

| 2.4.1.38 Download Address High (DEVAD = 1, Address = 0xA81A)                                     | 80         |

| 2.4.1.39 Download Data Low (DEVAD = 1, Address = 0xA81B)                          | 985.80 |

|-----------------------------------------------------------------------------------|--------|

| 2.4.1.40 Download Data High (DEVAD = 1, Address = 0xA81C)                         |        |

| 2.4.1.41 CTL LED1 MASK LOW (DEVAD = 1, Address = 0xA82C)                          |        |

| 2.4.1.42 CTL LED1 MASK EXT (DEVAD = 1, Address = 0xA8EF)                          |        |

| 2.4.1.43 CTL LED1 BLINK (DEVAD = 1, Address = 0xA82E)                             |        |

| 2.4.1.44 CTL LED2 MASK LOW (DEVAD = 1, Address = 0xA82F)                          |        |

| 2.4.1.45 CTL LED2 MASK EXT (DEVAD = 1, Address = 0xA8F0)                          |        |

| 2.4.1.46 CTL LED2 BLINK (DEVAD = 1, Address = 0xA831)                             |        |

| 2.4.1.47 CTL LED3 MASK LOW (DEVAD = 1, Address = 0xA832)                          |        |

| 2.4.1.48 CTL LED3 MASK EXT (DEVAD = 1, Address = 0xA8F1)                          | 83     |

| 2.4.1.49 CTL LED3 BLINK (DEVAD = 1, Address = 0xA834)                             |        |

| 2.4.1.50 CTL LED4 MASK LOW (DEVAD = 1, Address = 0xA835)                          | 84     |

| 2.4.1.51 CTL LED4 MASK EXT (DEVAD = 1, Address = 0xA8F2)                          | 85     |

| 2.4.1.52 CTL LED4 BLINK (DEVAD = 1, Address = 0xA837)                             | 85     |

| 2.4.1.53 CTL LED5 MASK LOW (DEVAD = 1, Address = 0xA838)                          | 85     |

| 2.4.1.54 CTRL LED5 MASK EXT (DEVAD = 1, Address = 0xA8F3)                         | 86     |

| 2.4.1.55 CTL LED5 BLINK (DEVAD = 1, Address = 0xA83A)                             | 86     |

| 2.4.1.56 PHYC_CTL_SLOW_CLK_CNT_HIGH (DEVAD = 1, Address = 0xA82B)                 | 87     |

| 2.4.1.57 PHYC_CTL_SLOW_CLK_CNT_LOW (DEVAD = 1, Address = 0xA82A)                  | 87     |

| 2.4.1.58 LED Control (DEVAD = 1, Address = 0xA83B)                                | 87     |

| 2.4.1.59 LED Control Source (DEVAD = 1, Address = 0xA83C)                         | 88     |

| 2.4.1.60 LED Control Source High (DEVAD = 1, Address = 0xA83D)                    | 89     |

| 2.4.1.61 LED Control 1 (DEVAD = 1, Address = 0xA8EC)                              | 89     |

| 2.4.1.62 10GBASE-T Tone Frequency (DEVAD = 1, Address = 0xA89E)                   | 90     |

| 2.4.1.63 10GBASE-T Number of Retrain (DEVAD = 1, Address = 0xA89F)                | 90     |

| 2.4.1.64 10GBASE-T Number of Linkdown (DEVAD = 1, Address = 0xA8A0)               | 90     |

| 2.4.1.65 10GBASE-T Number of Successful EMI Retrain (DEVAD = 1, Address = 0xA8A9) | 90     |

| 2.4.1.66 MDI Differential Level on Pair A (DEVAD = 1, Address = 0xA8AA)           | 90     |

| 2.4.1.67 MDI Differential Level on Pair B (DEVAD = 1, Address = 0xA8AB)           |        |

| 2.4.1.68 MDI Differential Level on Pair C (DEVAD = 1, Address = 0xA8AC)           |        |

| 2.4.1.69 MDI Differential Level on Pair D (DEVAD = 1, Address = 0xA8AD)           |        |

| 2.4.2 AutogrEEn Register Description (DEVAD = 1)                                  |        |

| 2.4.2.1 AutogrEEEn Control 1 Register (DEVAD = 1, Address = 0xA88A)               |        |

| 2.4.2.2 AutogrEEEn Threshold High Register (DEVAD = 1, Address = 0xA88C)          |        |

| 2.4.2.3 AutogrEEEn Threshold Low Register (DEVAD = 1, Address = 0xA88D)           | 92     |

| 2.4.2.4 AutogrEEEn Constant Latency Register (DEVAD = 1, Address = 0xA88E)        |        |

| 2.4.3 Fast Retrain Register Description (DEVAD = 1)                               |        |

| 2.4.3.1 Fast Retrain PMD IEEE Status Register (DEVAD = 1, Address = 0xA92B)       |        |

| 2.4.3.2 HiGig2 Enable Register (DEVAD = 1, Address = 0xA939)                      |        |

| 2.4.4 10GBASE-T Register Description (DEVAD = 3, PCS)                             | 93     |

|     | 2.4.4.1 PCS Control 1 Register (DEVAD = 3, Address = 0x0000)                      | MAN 23 |

|-----|-----------------------------------------------------------------------------------|--------|

|     | 2.4.4.2 PCS Status 1 Register (DEVAD = 3, Address = 0x0001)                       |        |

|     | 2.4.4.3 PCS Device Identifier Part 0 (DEVAD = 3, Address = 0x0002)                | 95     |

|     | 2.4.4.4 PCS Device Identifier Part 1 (DEVAD = 3, Address = 0x0003)                |        |

|     | 2.4.4.5 PCS Speed Ability (DEVAD = 3, Address = 0x0004)                           | 95     |

|     | 2.4.4.6 Devices 0 Package Register (DEVAD = 3, Address = 0x0005)                  | 95     |

|     | 2.4.4.7 Devices 1 Package Register (DEVAD = 3, Address = 0x0006)                  | 96     |

|     | 2.4.4.8 PCS Control 2 Register (DEVAD = 3, Address = 0x0007)                      | 97     |

|     | 2.4.4.9 10G PCS Status 2 Register (DEVAD = 3, Address = 0x0008)                   | 97     |

|     | 2.4.4.10 PCS Package Identifier 0 (DEVAD = 3, Address = 0x000E)                   | 98     |

|     | 2.4.4.11 PCS Package Identifier 1 (DEVAD = 3, Address = 0x000F)                   | 98     |

|     | 2.4.4.12 EEE Capability Register (DEVAD = 3, Address = 0x0014)                    | 98     |

|     | 2.4.4.13 10GBASE_T PCS_EEE_WAKE_ERR_CNT Register (DEVAD = 3, Address = 0x0016)    | 99     |

|     | 2.4.4.14 10GBASE_T PCS Status 1 (DEVAD = 3, Address = 0x0020)                     | 99     |

|     | 2.4.4.15 10GBASE_T PCS Status 2 (DEVAD = 3, Address = 0x0021)                     | 100    |

| 2.5 | AN Registers Descriptions (DEVAD = 7, AN)                                         | 100    |

|     | 2.5.1 10GBASE-T AN Control Register (DEVAD = 7, Address = 0x0000)                 | 100    |

|     | 2.5.2 10GBASE-T AN Status Register (DEVAD = 7, Address = 0x0001)                  | 100    |

|     | 2.5.3 10GBASE-T AN Device ID 1 Register (DEVAD = 7, Address = 0x0002)             | 101    |

|     | 2.5.4 10GBASE-T AN Device ID 2 Register (DEVAD = 7, Address = 0x0003)             | 101    |

|     | 2.5.5 10GBASE-T AN Device In Package 0 Register (DEVAD = 7, Address = 0x0005)     | 101    |

|     | 2.5.6 10GBASE-T AN Device In Package 1 Register (DEVAD = 7, Address = 0x0006)     | 101    |

|     | 2.5.7 10GBASE-T AN Package ID 0 Register (DEVAD = 7, Address = 0x000E)            | 101    |

|     | 2.5.8 10GBASE-T AN Package ID 1 Register (DEVAD = 7, Address = 0x000F)            | 102    |

|     | 2.5.9 10GBASE-T AN Advertisement 1 Register (DEVAD = 7, Address = 0x0010)         | 102    |

|     | 2.5.10 10GBASE-T AN LP BASE Page Ability 1 Register (DEVAD = 7, Address = 0x0013) | 102    |

|     | 2.5.11 10GBASE-T AN XNP Transmit 1 Register (DEVAD = 7, Address = 0x0016)         | 102    |

|     | 2.5.12 10GBASE-T AN XNP Transmit 2 Register (DEVAD = 7, Address = 0x0017)         | 103    |

|     | 2.5.13 10GBASE-T AN XNP Transmit 3 Register (DEVAD = 7, Address = 0x0018)         | 103    |

|     | 2.5.14 10GBASE-T AN LP XNP Ability 1 Register (DEVAD = 7, Address = 0x0019)       | 103    |

|     | 2.5.15 10GBASE-T AN LP XNP Ability 2 Register (DEVAD = 7, Address = 0x001A)       | 103    |

|     | 2.5.16 10GBASE-T AN LP XNP Ability 3 Register (DEVAD = 7, Address = 0x001B)       | 103    |

|     | 2.5.17 10GBASE-T AN Control (DEVAD = 7, Address = 0x0020)                         |        |

|     | 2.5.18 10GBASE-T AN Status (DEVAD = 7, Address = 0x0021)                          | 104    |

|     | 2.5.19 EEE Advertisement Register (DEVAD = 7, Address = 0x003C)                   | 105    |

|     | 2.5.20 EEE Advertisement 2 Register (DEVAD = 7, Address = 0x003E)                 | 106    |

|     | 2.5.21 EEE Link Partner Advertisement 2 Register (DEVAD = 7,                      | 400    |

|     | Address = 0x003F)                                                                 |        |

|     | 2.5.22 Multi-GBASET AN Control 2 Register (DEVAD = 7, Address = 0x0040)           |        |

|     | 2.5.23 Multi-GBASET AN Status 2 Register (DEVAD = 7, Address = 0x0041)            | 107    |

|     | 2.5.24 EEE Link Partner Advertisement Register (DEVAD = 7, Address = 0x003D)               | 107 |

|-----|--------------------------------------------------------------------------------------------|-----|

| 2.6 | 1000BASE-T/100BASE-TX Registers Descriptions (DEVAD = 7, PCS, PMA)                         |     |

|     | 2.6.1 1000BASE-T/100BASE-TX MII Control (DEVAD = 7, Address = 0xFFE0)                      | 108 |

|     | 2.6.2 1000BASE-T/100BASE-TX MII Status (DEVAD = 7, Address = 0xFFE1)                       |     |

|     | 2.6.3 1000BASE-T/100BASE-TX PHY Identifier (DEVAD = 7, Address = 0xFFE2, Address = 0xFFE3) |     |

|     | 2.6.4 Copper Auto-Negotiation Advertisement (DEVAD = 7, Address = 0xFFE4)                  |     |

|     | 2.6.4.1 Next Page                                                                          |     |

|     | 2.6.4.2 Remote Fault                                                                       | 112 |

|     | 2.6.4.3 Reserved Technology                                                                | 112 |

|     | 2.6.4.4 Asymmetric Pause                                                                   | 113 |

|     | 2.6.4.5 Pause Capable                                                                      | 113 |

|     | 2.6.4.6 100BASE-T4 Capable                                                                 | 113 |

|     | 2.6.4.7 100BASE-TX Full-Duplex Capable                                                     | 113 |

|     | 2.6.4.8 100BASE-TX Half-Duplex Capable                                                     | 113 |

|     | 2.6.4.9 Selector Field                                                                     | 113 |

|     | 2.6.5 Copper Auto-Negotiation Link Partner Ability (DEVAD = 7, Address = 0xFFE5)           | 113 |

|     | 2.6.5.1 Next Page                                                                          | 114 |

|     | 2.6.5.2 Acknowledge                                                                        | 114 |

|     | 2.6.5.3 Remote Fault                                                                       | 114 |

|     | 2.6.5.4 Reserved Technology                                                                | 114 |

|     | 2.6.5.5 Asymmetric Pause                                                                   | 114 |

|     | 2.6.5.6 Pause Capable                                                                      | 115 |

|     | 2.6.5.7 100BASE-T4 Capable                                                                 | 115 |

|     | 2.6.5.8 100BASE-TX Full-Duplex Capable                                                     | 115 |

|     | 2.6.5.9 100BASE-TX Half-Duplex Capable                                                     | 115 |

|     | 2.6.5.10 Protocol Selector Field                                                           | 115 |

|     | 2.6.6 Copper Auto-Negotiation Expansion (DEVAD = 7, Address = 0xFFE6)                      | 115 |

|     | 2.6.7 Copper Next Page Transmit (DEVAD = 7, Address = 0xFFE7)                              | 116 |

|     | 2.6.7.1 Next Page                                                                          | 116 |

|     | 2.6.7.2 Message Page                                                                       | 116 |

|     | 2.6.7.3 Acknowledge2                                                                       | 116 |

|     | 2.6.7.4 Toggle                                                                             | 117 |

|     | 2.6.7.5 Message/Unformatted Code Field                                                     | 117 |

|     | 2.6.8 Copper Link Partner Received Next Page (DEVAD = 7, Address = 0xFFE8)                 | 117 |

|     | 2.6.9 1000BASE-T Control (DEVAD = 7, Address = 0xFFE9)                                     | 118 |

|     | 2.6.10 1000BASE-T Status (DEVAD = 7, Address = 0xFFEA)                                     | 119 |

|     | 2.6.10.1 Master/Slave Configuration Fault                                                  | 119 |

|     | 2.6.10.2 Master/Slave Configuration Resolution                                             | 119 |

|     | 2.6.10.3 Local Receiver Status                                                             |     |

|     | 2.6.10.4 Remote Receiver Status                                                            | 119 |

| 2.6.10.5 1000BASE-T Full-Duplex Capability                                    | 184 / 3308 PB <sup>0</sup> |

|-------------------------------------------------------------------------------|----------------------------|

| 2.6.10.6 1000BASE-T Half-Duplex Capability                                    |                            |

| 2.6.11 1000BASE-T/100BASE-TX IEEE Extended Status (DEVAD = 7, Address = 0     |                            |

| 2.6.11.1 1000BASE-X Full-Duplex Capable                                       | •                          |

| 2.6.11.2 1000BASE-X Half-Duplex Capable                                       |                            |

| 2.6.11.3 1000BASE-T Full-Duplex Capable                                       |                            |

| 2.6.11.4 1000BASE-T Half-Duplex Capable                                       |                            |

| 2.6.12 1000BASE-T/100BASE-TX PHY Extended Control (DEVAD = 7, Address =       |                            |

| 2.6.12.1 Disable Automatic MDI Crossover                                      | •                          |

| 2.6.12.2 Transmit Disable                                                     |                            |

| 2.6.12.3 Bypass 4B/5B Encoder/Decoder (100BASE-TX)                            | 122                        |

| 2.6.12.4 Bypass Scrambler/Descrambler (100BASE-TX)                            | 122                        |

| 2.6.12.5 Bypass MLT3 Encoder/Decoder (100BASE-TX)                             | 122                        |

| 2.6.12.6 Bypass Receive Symbol Alignment (100BASE-TX)                         |                            |

| 2.6.12.7 Reset Scrambler (100BASE-TX)                                         | 122                        |

| 2.6.12.8 Enable LED Traffic Mode                                              | 122                        |

| 2.6.12.9 Force LEDs On                                                        | 122                        |

| 2.6.12.10 Force LEDs Off                                                      | 122                        |

| 2.6.13 1000BASE-T/100BASE-TX PHY Extended Status (DEVAD = 7, Address = 0      | xFFF1)123                  |

| 2.6.13.1 Auto-Negotiation BASE Page Selector Field Mismatch                   | 123                        |

| 2.6.13.2 Ethernet@Wirespeed Downgrade                                         | 123                        |

| 2.6.13.3 MDI Crossover State                                                  | 124                        |

| 2.6.13.4 Remote Receiver Status                                               | 124                        |

| 2.6.13.5 Local Receiver Status                                                | 124                        |

| 2.6.13.6 Locked                                                               | 124                        |

| 2.6.13.7 Link Status                                                          | 124                        |

| 2.6.13.8 CRC Error Detected                                                   | 124                        |

| 2.6.13.9 Carrier Extension Error Detected                                     | 124                        |

| 2.6.13.10 Bad SSD Detected (False Carrier)                                    |                            |

| 2.6.13.11 Bad ESD Detected (Premature End)                                    | 124                        |

| 2.6.13.12 Receive Error Detected                                              | 125                        |

| 2.6.13.13 Transmit Error Detected                                             | 125                        |

| 2.6.13.14 Lock Error Detected                                                 | 125                        |

| 2.6.13.15 MLT3 Code Error Detected                                            | 125                        |

| 2.6.14 1000BASE-T/100BASE-TX Receive Error Counter (DEVAD = 7, Address = 0    | 0xFFF2)125                 |

| 2.6.14.1 Receive Error Counter                                                | 125                        |

| 2.6.15 1000BASE-T/100BASE-TX False Carrier Sense Counter (DEVAD = 7, Address) | •                          |

| 2.6.15.1 False Carrier Sense Counter                                          |                            |

| 2.6.16 1000BASE-T/100BASE-TX Receiver NOT_OK Counter (DEVAD = 7, Address      | ss = FFF4h)126             |

| 2.6.16.1 Local Receiver NOT_OK Counter                                        | 126                        |

| 2.6.16.2 Remote Receiver NOT_OK Counter                                                                  | 126 |

|----------------------------------------------------------------------------------------------------------|-----|

| 2.6.17 1000BASE-T/100BASE-TX Expansion Register Access (DEVAD = 7, Address = 0xFFF7)                     |     |

| 2.6.17.1 Expansion Register Accessed                                                                     |     |

| 2.6.18 1000BASE-T/100BASE-TX Auxiliary Control Shadow Value Access Register (DEVAD = 7, Address = FFF8h) | 127 |

| 2.6.19 1000BASE-T/100BASE-TX Auxiliary Control (DEVAD = 7, Address = 0xFFF8, Shadow Value 000b)          | 128 |

| 2.6.20 1000BASE-T/100BASE-TX Power/MII Control (DEVAD = 7, Address = 0xFFF8, Shadow Value 010b)          | 129 |

| 2.6.21 1000BASE-T/100BASE-TX Misc. Test Register R (DEVAD = 7, Address = 0xFFF8, Shadow Value 100b)      | 130 |

| 2.6.22 1000BASE-T/100BASE-TX Misc. Control (DEVAD = 7, Address = 0xFFF8, Shadow Value 111b)              | 131 |

| 2.6.22.1 Write Enable (Bits 11:3)                                                                        | 132 |

| 2.6.22.2 Shadow Register Read Selector                                                                   | 132 |

| 2.6.22.3 Packet Counter Mode                                                                             | 132 |

| 2.6.22.4 Force Auto-MDIX Mode                                                                            | 132 |

| 2.6.22.5 Ethernet@Wirespeed Enable                                                                       | 132 |

| 2.6.22.6 Shadow Register Select                                                                          | 133 |

| 2.6.23 1000BASE-T/100BASE-TX Auxiliary Status Summary (DEVAD = 7, Address = 0xFFF9)                      | 133 |

| 2.6.23.1 Auto-Negotiation Complete                                                                       | 134 |

| 2.6.23.2 Auto-Negotiation Complete Acknowledge                                                           | 134 |

| 2.6.23.3 Auto-Negotiation Acknowledge Detect                                                             | 134 |

| 2.6.23.4 Auto-Negotiation Ability Detect                                                                 | 134 |

| 2.6.23.5 Auto-Negotiation Next Page Wait                                                                 | 134 |

| 2.6.23.6 Auto-Negotiation HCD (Current Operating Speed and Duplex Mode)                                  | 134 |

| 2.6.23.7 Parallel Detection Fault                                                                        |     |

| 2.6.23.8 Remote Fault                                                                                    | 135 |

| 2.6.23.9 Auto-Negotiation Page Received                                                                  | 135 |

| 2.6.23.10 Link Partner Auto-negotiation Ability                                                          |     |

| 2.6.23.11 Link Partner Next Page Ability                                                                 |     |

| 2.6.23.12 Link Status                                                                                    |     |

| 2.6.23.13 Pause Resolution in the Receive Direction and Transmit Direction                               |     |

| 2.6.24 1000BASE-T/100BASE-TX Register 1Ch Access (DEVAD = 7, Address = 0xFFFC)                           |     |

| 2.6.25 1000BASE-T/100BASE-TX Spare Control 2                                                             |     |

| (DEVAD = 7, Address = 0xFFFC, Shadow Value 00100b)                                                       | 136 |

| 2.6.25.1 Write Enable                                                                                    | 137 |

| 2.6.25.2 Shadow Register Selector                                                                        | 137 |

| 2.6.25.3 Ethernet@Wirespeed Retry Limit                                                                  | 137 |

| 2.6.25.4 Energy Detect on INTR Pin                                                                       | 137 |

| 2.6.26 1000BASE-T/100BASE-TX Auto Power-Down (DEVAD = 7, Address = 0xFFFC, Shadow Value 01010b)          | 137 |

|     | 2.6.27 1000BASE-T/100BASE-TX Master/Slave Seed (DEVAD = 7, Address = FFFDh) | 15867339858                     |

|-----|-----------------------------------------------------------------------------|---------------------------------|

|     | 2.6.27.1 Enable Shadow Register                                             |                                 |

|     | 2.6.27.2 Master/Slave Seed Match                                            |                                 |

|     | 2.6.27.3 Link Partner Repeater/DTE Bit                                      |                                 |

|     | 2.6.27.4 Link Partner Manual Master/Slave Configuration Value               |                                 |

|     | 2.6.27.5 Link Partner Manual Master/Slave Configuration Enable              |                                 |

|     | 2.6.27.6 Local Master/Slave Seed Value                                      |                                 |

|     | 2.6.28 1000BASE-T/100BASE-TX HCD Status (DEVAD = 7, Address = FFFD          | Ph)139                          |

|     | 2.6.28.1 Enable Shadow Register                                             | 140                             |

|     | 2.6.28.2 Ethernet@Wirespeed Disable Gigabit Advertising                     | 140                             |

|     | 2.6.28.3 Ethernet@Wirespeed Disable 100BASE-TX Advertising                  | 140                             |

|     | 2.6.28.4 Ethernet@Wirespeed Downgrade                                       | 140                             |

|     | 2.6.28.5 HCD 1000BASE-T FDX                                                 | 140                             |

|     | 2.6.28.6 HCD 1000BASE-T                                                     | 140                             |

|     | 2.6.28.7 HCD 100BASE-TX FDX                                                 | 140                             |

|     | 2.6.28.8 HCD 100BASE-T                                                      | 140                             |

|     | 2.6.28.9 HCD 1000BASE-T FDX (Link Never Came Up)                            | 141                             |

|     | 2.6.28.10 HCD 1000BASE-T (Link Never Came Up)                               | 141                             |

|     | 2.6.28.11 HCD 100BASE-TX FDX (Link Never Came Up)                           |                                 |

|     | 2.6.28.12 HCD 100BASE-TX (Link Never Came Up)                               |                                 |

|     | 2.6.29 1000BASE-T/100BASE-TX Test Register 1 (DEVAD = 7, Address = FF       |                                 |

|     | 2.6.30 Expansion Register 00h: Receive/Transmit Packet Counter              |                                 |

|     | 2.6.31 Expansion Register 42h: Operating Mode Status                        |                                 |

|     | 2.6.32 Expansion Register 46h: Pattern Generator Status                     |                                 |

| 2.7 | XFI Registers                                                               |                                 |

|     | 2.7.1 XFI PMD_PMA Register Description (DEVAD = 1 PMA/PMD)                  |                                 |

|     | 2.7.1.1 XFI 10GBASE-R PMD Control Register (DEVAD = 1, Address = 0          |                                 |

|     | 2.7.1.2 XFI 10GBASE-R Status Register (DEVAD = 1, Address = 0x0001          |                                 |

|     | 2.7.1.3 XFI 10GBASE-R PMD Speed Ability Register (DEVAD = 1, Addre          |                                 |

|     | 2.7.1.4 XFI 10GBASE-R Device in Package 1 Register (DEVAD = 1, Add          | ·                               |

|     | 2.7.1.5 XFI 10GBASE-R Device in Package 2 Register (DEVAD = 1, Add          | ,                               |

|     | 2.7.1.6 XFI 10GBASE-R PMD Control 2 Register (DEVAD = 1, Address =          | ,                               |

|     | 2.7.1.7 XFI 10GBASE-R Status 2 Register (DEVAD = 1, Address = 0x000         | •                               |

|     | 2.7.1.8 XFI 10GBASE-R PMD Transmit Disable Register (DEVAD = 1, Ad          | •                               |

|     | 2.7.1.9 XFI 10GBASE-R PMD Receive Signal Detect Register (DEVAD =           | ,                               |

|     | 2.7.1.10 XFI 10GBASE-R PMD Extended Ability Register (DEVAD = 1, A          | ,                               |

|     | 2.7.1.11 XFI_TX_prbs_gen_config: PRBS Generator Control (DEVAD = 1          | ,                               |

|     | 2.7.1.12 XFI_RX_prbs_chk_config: PRBS Checker Control (DEVAD = 1,           | •                               |

|     | 2.7.1.13 XFI_RX_prbs_chk_lock_status: PRBS Checker LOCK Status (D           | 'EVAD = 1, Address = 0xD0D9)150 |

| 2.7.1.14 XFI_RX_prbs_chk_err_cnt_msb_status: PRBS Checker Error Counter MSB Status (DEV/Address = 0xD0DA)   |     |

|-------------------------------------------------------------------------------------------------------------|-----|

| 2.7.1.15 XFI_RX_prbs_chk_err_cnt_lsb_status: PRBS Checker Error Counter LSB Status (DEVAL Address = 0xD0DB) |     |

| 2.7.2 XFI PCS Register Description (DEVAD = 3 PHY XS)                                                       |     |

| 2.7.2.1 XFI 10GBASE-R PCS Control 1 Register (DEVAD = 3, Address = 0x0000)                                  | 151 |

| 2.7.2.2 XFI 10GBASE-R Status 1 Register (DEVAD = 3, Address = 0x0001)                                       | 151 |

| 2.7.2.3 XFI 10GBASE-R Speed Ability Register (DEVAD = 3, Address = 0x0004)                                  | 151 |

| 2.7.2.4 XFI 10GBASE-R Devices in Package 1 Register (DEVAD = 3, Address = 0x0005)                           | 152 |

| 2.7.2.5 XFI 10GBASE-R Device in Package 2 Register (DEVAD = 3, Address = 0x0006)                            | 152 |

| 2.7.2.6 XFI 10GBASE-R PCS Control 2 Register (DEVAD = 3, Address = 0x0007)                                  | 152 |

| 2.7.2.7 XFI 10GBASE-R PCS Status 2 Register (DEVAD = 3, Address = 0x0008)                                   | 152 |

| 2.7.2.8 XFI 10GBASE-R PCS Status 1 (DEVAD = 3, Address = 0x0020)                                            | 153 |

| 2.7.2.9 XFI 10GBASE-R Status 2 (DEVAD = 3, Address = 0x0021)                                                | 153 |

| 2.8 User-Defined Registers (Device = 30)                                                                    |     |

| 2.8.1 AutogrEEEn Control 1 Register (DEVAD = 30, Address = 0x400A)                                          | 154 |

| 2.8.2 AutogrEEEn Threshold High Register (DEVAD = 30, Address = 0X400B)                                     | 154 |

| 2.8.3 AutogrEEEn Threshold Low Register (DEVAD = 30, Address = 0X400C)                                      |     |

| 2.8.4 Status Register (DEVAD = 30, Address = 0x400D)                                                        | 154 |

| 2.8.5 User Request 1 Status Register (DEVAD = 30, Address = 0x400E)                                         |     |

| 2.8.6 Firmware Rev Register (DEVAD = 30, Address = 0x400F)                                                  |     |

| 2.8.7 Firmware Date Register (DEVAD = 30, Address = 0x4010)                                                 |     |

| 2.8.8 Config Strap Pins Registers (DEVAD = 30, Address = 0x401A)                                            |     |

| 2.8.9 Strap Pins Registers (DEVAD = 30, Address = 0x401C)                                                   |     |

| 2.8.10 SYNC_E Configuration 1 (DEVAD=30, Address = 0x404F)                                                  |     |

| 2.8.11 User Control Register (DEVAD = 30 Address 0x4191)                                                    |     |

| 2.8.12 SYNC Common CFG Register (DEVAD = 30, Address = 0xA04C)                                              |     |

| 2.8.13 MDIO Control 0 Register (DEVAD = 30, Address = 0x4110)                                               |     |

| 2.8.14 MDIO Control 1 Register (DEVAD = 30, Address = 0x4111)                                               |     |

| 2.8.15 MDIO Control 2 Register (DEVAD = 30, Address = 0x4112)                                               |     |

| 2.8.16 MDIO Control 3 Register (DEVAD = 30, Address = 0x4113)                                               |     |

| 2.8.17 MDIO Control 4 Register (DEVAD = 30, Address = 0x4114)                                               |     |

| 2.8.18 MDIO Control 5 Register (DEVAD = 30, Address = 0x4115)                                               |     |

| Chapter 3: Pin Descriptions                                                                                 | 159 |

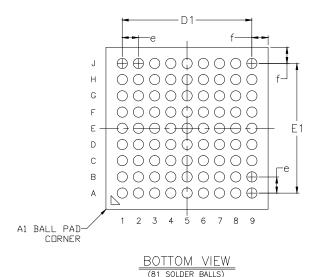

| 3.1 I/O Pin Assignments and Descriptions                                                                    | 159 |

| 3.2 Pin List                                                                                                |     |

| 3.2.1 Pin List by Ball Number                                                                               |     |

| 3.2.2 Pin List by Signal Name                                                                               |     |

| 3.3 Pinout Diagram                                                                                          | 165 |

| Chapter 4: Electrical Characteristics                                                                       | 166 |

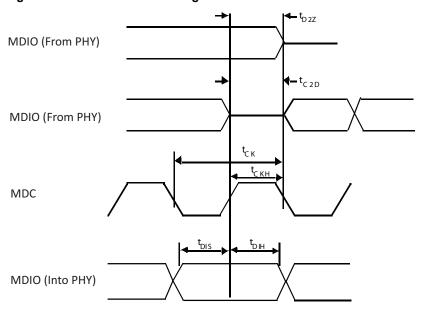

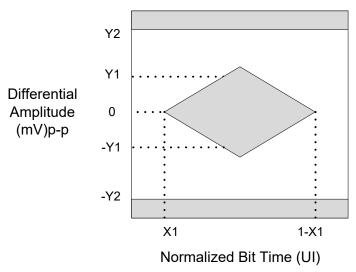

| 4.1 Parameters and Timing                                                              | 1.586./33.985.166 |

|----------------------------------------------------------------------------------------|-------------------|

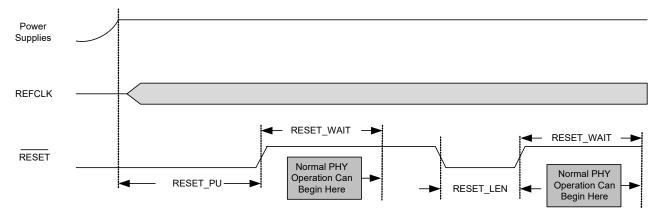

| 4.2 Reset Timing                                                                       |                   |

| Chapter 5: Thermal Characteristics                                                     | 174               |

| 5.1 Package                                                                            |                   |

| 5.2 External Heat Sink and Thermal Interface                                           | 174               |

| 5.3 Junction Temperature Estimation and $Psi_{JT}$ Versus Theta <sub>JC</sub> Overview | 175               |

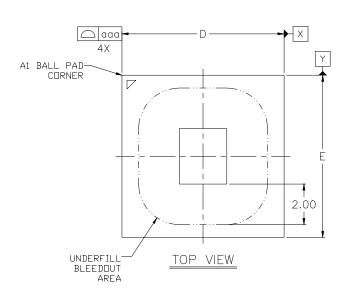

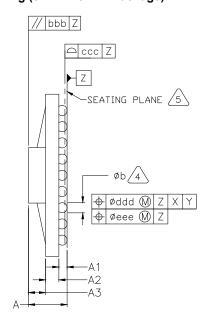

| Chapter 6: Mechanical Information                                                      | 176               |

| 6.1 Package Outline                                                                    | 176               |

| 6.2 RoHS-Compliant Packaging                                                           | 177               |

| Chapter 7: Ordering Information                                                        | 178               |

| Glossary                                                                               | 179               |

| Revision History                                                                       | 180               |

| 84891L-DS100; June 15, 2018                                                            | 180               |

## 15867339858

## **Chapter 1: Functional Description**

### 1.1 Overview

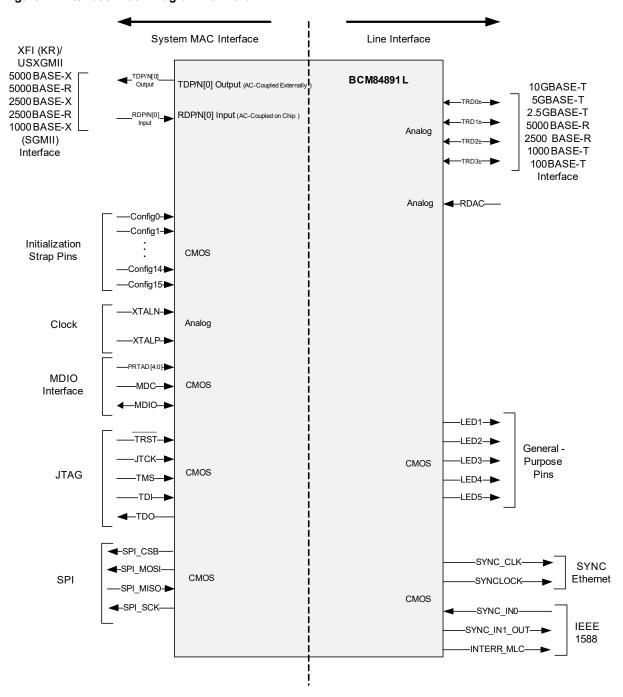

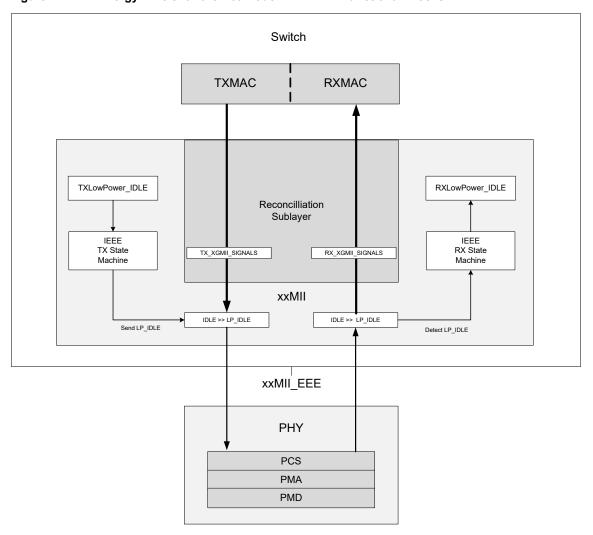

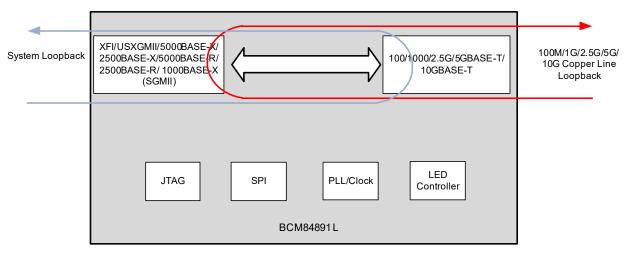

The figure below shows the system MAC and line interface on the BCM84891L.

Figure 2: Interface Block Diagram Per-Port

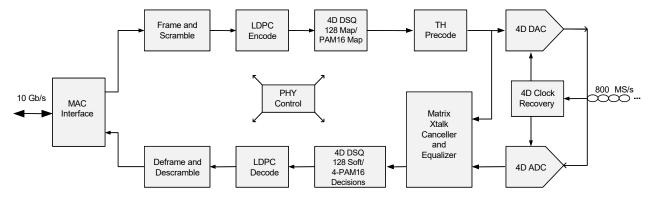

The figure below shows the major 10G/5G/2.5GBASE-T functions of the BCM84891L.

Figure 3: BCM84891L 10GBASE-T/5G/2.5GBASE-T Block Diagram

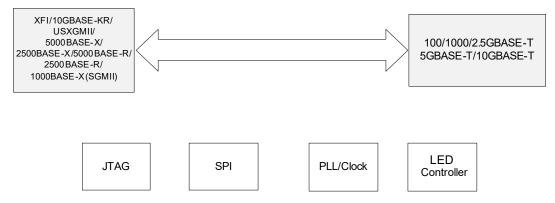

The figure below shows the BCM84891L data path block diagram.

Figure 4: Data Path Block Diagram

### 1.2 Device Functions

The BCM84891L is a 10GBASE-T/1000BASE-T/100BASE-TX transceiver that performs all the physical layer (PHY) interface function for 10GBASE-T, 1000BASE-T, 1000BASE-T Ethernet on Category 6, 6A, or 7 twisted-pair cable. 5GBASE-T, 2.5GBASE-T, 1000BASE-T, and 100BASE-TX operations are supported on Category 5e UTP. The BCM84891L connects to a Media Access Controller (MAC) or switch controller through XFI/10GBASE-KR or USXGMII for 10GBASE-T, USXGMII, 5000BASE-X, 5000BASE-R, or 5G rate over XFI for 5GBASE-T USXGMII, 2500BASE-X, 2500BASE-R, or 2.5G rate over XFI for 2.5GBASE-T and USXGMII, 1000BASE-X (SGMII) for 1000BASE-TX.

The device is fully compliant with the IEEE 802.3 standard for 10GBASE-T, 1000BASE-T, and 100BASE-T. Operation of 5GBASE-T and 2.5GBASE-T are compliant to IEEE 802.3bz. It connects to twisted-pair wiring of the network through isolation transformers. The BCM84891L can be programmed to auto-negotiate its operating speed based on the capabilities advertised by the link partner.

The BCM84891L device adheres to Broadcom's quality procedures and meets or exceeds the performance and functionality tested as part of a comprehensive product characterization, qualification, and functional verification process.

## 1.3 Operation Modes

## 15867339858

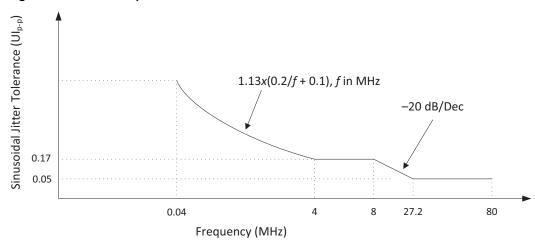

The BCM84891L supports XFI/USXGMII/5000BASE-X/2500BASE-X/1000BASE-X (SGMII)-to-Copper (10GBASE-T/5GBASE-T/2.5GBASE-T/1000BASE-T/100BASE-TX). Figure 5 shows the supported configuration for the XFI/USXGMII/5000BASE-X/2500BASE-X/1000BASE-X (SGMII)-to-Copper operation mode.

Figure 5: Functional Block Architecture for the XFI (10GBASE-KR)/2500BASE-X/1000BASE-X(SGMII)-to-Copper Configuration

### 1.4 10GBASE-T

The BCM84891L supports the 10GBASE-T transmission rate, per the IEEE P802.3an standard.

#### 1.4.1 Transmit Path

The transmitter path collects the 64-bit parallel data stream at the XGMII interface and reformats the data into 10GBASE-T/1000BASE-T over four twisted-pairs.

#### 1.4.1.1 Scramble and Frame

Scrambling or randomizing of the transmit data is necessary to minimize baseline wander and ensure proper operation of adaptive receiver subsystems, such as clock recovery and equalization. All data entering the PHY is scrambled by a 58-bit self-synchronizing scrambler. With continuous 10 Gb/s operation, this scrambler does not repeat more often than once every 55 years.

PHY-level frames are not visible to higher layers but are necessary to allow for proper synchronization and alignment of Low-Density Parity-Check (LDPC) blocks between the transmitter and receiver. PHY-level frames contain data from 50 consecutive 65-bit XGMII data/control blocks. A CRC-8 is computed across  $50 \times 65 = 3250$  bits and appended to the frame. One additional bit is added for vendor-specific purposes, bringing the total PHY-level frame payload to  $(1 + 50) \times (65 + 8) = 3259$  bits.

#### 1.4.1.2 LDPC Encode

15867339858

A low-density parity check code is an error correcting code, a method of transmitting a message over a noisy transmission channel. The BCM84891L adds 325 parity bits to blocks of 1723 data bits. This block encoding operation is equivalent to a matrix multiplication of c = xG, where x is a 1723-bit input vector [x0, x1, ..., x1772], c is a 2048 output code vector [c0, c1, ..., c2043], and G is the code generator matrix.

From the PHY frame payload of 3259 bits, 1723 bits are encoded by the LDPC encoder and 1536 bits remain uncoded. The 325 parity bits are added to the 3259-bit payload for a total encoded PHY frame size of 3584 bits. Code block boundaries are recovered at the receiver through PHY frame boundaries.

#### 1.4.1.3 DSQ128 Map (10GBASE-T)

The 3584 bit encoded PHY frame contains  $3584 \div 7 = 512$ , 7-bit DSQ128 symbols. Each 7-bit symbol maps to a single point in a two-dimensional symbol constellation. Each DSQ128 symbol is transmitted in two consecutive sample intervals: first the I value, then the Q value. The I-Q ordering is aligned with the PHY frame boundary so that it can be recovered by the receiver. Each 512 symbol PHY frame is divided across four-wire pairs. In each symbol interval, four symbols are transmitted in parallel across the four wires: either four I values or four Q values.

#### 1.4.1.4 PAM16 Mapping (IEEE 802.3bz)

The 2048 bit encoded PHY frame contains  $2048 \div 4 = 512$ , 4-bit gray-coded PAM16 symbols. Each 4-bit symbol maps to a single point in a one-dimensional symbol constellation. The frame structure for 2.5G and 5G modes are identical except the symbol duration is 320 ns and 640 ns for 5G and 2.5G, respectively. Each 512 symbol PHY frame is divided across four-wire pairs. In each symbol interval, four PAM16 symbols are transmitted in parallel across the four wires.

#### 1.4.1.5 Tomlinson-Harashima Precode

Each dimension (four I values or four Q values) of the four channel symbols from the 4D DSQ128 mapper is passed through a Tomlinson-Harashima Precoder (THP). The THP is similar in structure to a Decision-Feedback Equalizer (DFE), but it is used in the transmitter rather than the receiver to avoid DFE error propagation issues. The coefficient values for the THP are determined as part of the link start-up sequence and remain fixed during data transfer.

#### 1.4.1.6 DAC

Each of the four outputs from the precoders are converted to an analog signal using integrated digital-to-analog converters (DAC). The DAC drives the  $100\Omega$  twisted-pair cable (through a transformer) with a differential signal. The average transmit power is 4.2 dBm for 100m (or greater) cables and backs off in value as the cable length is reduced.

#### 1.4.2 Receive Path

The receiver path accepts 10GBASE-T framing over four twisted-pairs and reformats the data into a 64-bit parallel data stream at the XGMII interface.

#### 1.4.2.1 Four-Channel ADC

The signal received on each of the four wire pairs is converted to a digital representation by integrated analog-to-digital converters (ADC).

#### 1.4.2.2 Clock Recovery

15867339858

The optimal sampling instant for each of the four ADCs is determined by the clock recovery circuit. In slave mode, the frequency and phase are derived from the received data, so that the slave is frequency- and phase-locked with the master.

#### 1.4.2.3 Matrix Crosstalk Canceler and Equalizer

The major cancellable/suppressible signal impairments are crosstalk within and between the four-wire pairs and intersymbol interference (ISI) caused by the insertion loss of a wire pair. Each receiver processes crosstalk from four local transmitters: three transmitters couple through near-end crosstalk (NEXT) channels and one transmitter (on the same wire) couple through the echo channel (echo is caused by the non-ideal return loss of the various components of the channel). The four crosstalk sources per each of the four receivers result in a 4x4 matrix crosstalk channel connecting the four local transmitters to the four local receivers. Adaptive matrix crosstalk cancellation removes the crosstalk from the signal. The matrix crosstalk canceler continuously adapts to track changes in the crosstalk and echo channels.

Each local receiver is connected to a remote transmitter by a direct channel (the wire) and to three other remote transmitters by crosstalk channels. These are also called far-end crosstalk (FEXT) channels. This arrangement operates as a 4x4 matrix channel connecting the four local receivers to the four remote transmitters. Adaptive matrix equalization counters the effects of the matrix signal channel. The matrix equalizer continuously adapts to track changes in the FEXT and ISI channels.

#### 1.4.2.4 Echo Canceler

Because of simultaneous bidirectional transmission of data on each cable pair in 10G/5G/2.5GBASE-T, echo impairments from the local transmitters are present at each receiver. A digital echo canceler subtracts an estimate of the echo from the received signal. The digital echo canceler coefficients are adaptive to track the varying echo transfer function caused by different channels, transmitters, cable geometry, and environmental conditions.

#### 1.4.2.5 Four-Channel DSQ128 Soft LDP Decision and LDPC Decoder (10GBASE-T)

The objective of matrix equalization, matrix crosstalk cancellation, and clock recovery processes is to reconstruct, as closely as possible, the original DSQ128 symbol transmitted by the link partner. The LDPC decoding algorithm uses soft decision decoding to greatly aid the correct detection of a block of received symbols.

At the transmitter, the LDPC encoder combines with the DSQ128 symbol mapper to set the LDPC block (PHY frame) of data sent. The LDPC decoder uses soft decisions to recover the LDPC block data sent. DSQ128 symbols are demapped into 7-bit data. A CRC-8 is computed across the recovered data bits in each PHY frame and compared to the transmitted value to detect block errors.

#### 1.4.2.6 Four-Channel PAM16 Soft LDP Decision and LDPC Decoder (IEEE 802.3bz)

The objective of the matrix equalization, matrix crosstalk cancellation, and the clock recovery processes is to reconstruct, as closely as possible similar to 10GBASE-T, where the original PAM16 symbol is transmitted by the link partner. The LDPC decoding algorithm uses soft decision decoding to greatly aid the correct detection of a block of received symbols.

At the transmitter, the LDPC encoder combines with the PAM16 symbol mapper to set the LDPC block (PHY frame) of data sent. The LDPC decoder uses soft decisions to recover the LDPC block data sent. PAM16 symbols are demapped into 4-bit data.

#### 1.4.2.7 Deframe and Descramble

## 15867339858

After LDPC decoding, PHY-level framing is no longer required as PHY-level frames are not visible to higher layers. All non-payload bits are removed by the deframing operation prior to transmission to the MAC. Each recovered PHY-level frame contains sufficient payload data to create 50 consecutive 65-bit XGMII data/control blocks. The recovered payload data bits are descrambled with the same 58-bit scrambler polynomial used at the transmitter. The device uses a side-stream scrambler that is synchronized by the Physical Coding Sublayer (PCS) receive block.

# 1.5 XFI (10GBASE-KR)/USXGMII/5000BASE-X/2500BASE-X/5000BASE-R/2500BASE-R

The XFI (10GBASE-KR)/5000BASE-X/2500BASE-X/5000BASE-R/2500BASE-R is a high-speed serial interface with fully integrated 10 Gb/2.5 Gb/1 Gb serial Ethernet PCS and Physical Media Attachment (PMA) functions. It includes 64-bit/66-bit coding and 8B/10B coding, block scrambling, a Clock Multiplication Unit (CMU), and Clock and Data Recovery (CDR). The XFI (10GBASE-KR) interface adheres to INF-8077i SFF standard.

NOTE: 10GBASE-KR mode is disabled as default. When KR mode is enabled through the command handler, 5000BASE-X/2500BASE-X is not supported and the user should enable 2.5 Gb rate over the XFI interface signals in 10GBASE-KR mode.

#### 1.5.1 Transmit Path

At the XGMII interface, the XFI (10GBASE-KR) receives data that is transmitted serially towards the MAC side (the system side). Data gets 64-bit/66-bit encoded, then scrambled before being transmitted.

#### 1.5.1.1 64-Bit/66-Bit Encoder

The PCS on the XFI (10GBASE-KR) side encodes 64-bit data into 66-bit blocks and inserts the necessary control codes required for transmission across the communication link. The encoding, defined by the IEEE 802.3ae clause 49 for transmission code, ensures sufficient transitions are present in the PHY bit stream to make clock recovery possible at the receiver.

#### 1.5.1.1.1 Scrambler

Data blocks received from the 64-bit/66-bit encoder are passed through a scrambler polynomial and then passed onto the gearbox.

#### 1.5.1.2 XFI (10GBASE-KR) Ingress TX Gearbox

The TX gearbox is a buffer that prepares the 66-bit block data for efficient serialization in the PMA sublayer.

#### 1.5.1.3 XFI (10GBASE-KR) Ingress TX Serializer

Data is read out of the gearbox and then converted to a 10.3125 Gb/s serial stream and driven off-chip. Bit 0 of frame 0 (LSB) is shifted out first.

#### 1.5.1.4 XFI (10GBASE-KR) Clock Multiplication Unit

15867339858

The XFI (10GBASE-KR) CMU has a PLL that generates the 10.3125/3.125 GHz clock by multiplying the external reference clock (either 50 MHz or 156.25 MHz).

#### 1.5.1.5 XFI (10GBASE-KR) CMU Lock Detect

The BCM84891L contains a lock detect circuit, which monitors the frequency of the internal VCO.

#### 1.5.1.6 XFI (10GBASE-KR) CMOS Differential Serial Output Interface

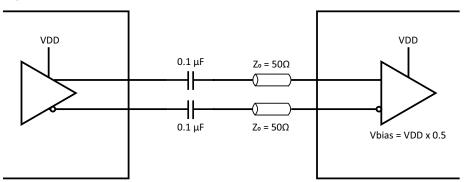

The CMOS differential serial outputs (XFI\_OP/N) must be AC-coupled. The CMOS differential outputs are powered at +1.0V. These high-speed CMOS differential outputs consist of a differential pair designed to drive a  $100\Omega$  differential transmission line. The output driver is back terminated to  $50\Omega$  on-chip, to snub any reflections.

Provisions are provided through the Management Interface for deactivating the output transmitter by transmitting a constant logical low level (0) at the XFI (10GBASE-KR) output.

**NOTE:** CMOS differential output drivers do not have on-chip built-in AC-Coupling. External AC-coupling should be used to drive the receiver input device. AC-coupling prevents voltage drops across the input devices of the receiver when the input signals are sourced from a device with a higher operating voltage.

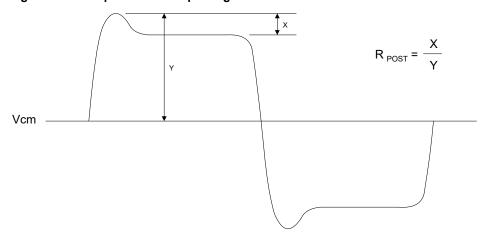

The CMOS differential output includes a four-tap (pre, main, post1, and post2 cursor) preemphasis control. To configure a port with a particular preemphasis setting, see Table 1. To use typical values for the XFI/10GBASE-KR transmit preemphasis, no special register setting or command is required.

Figure 6: Preemphasis with Repeating Pattern of Four 1s and Four 0s

**Table 1: Main and Post Cursor Settings**

| Main Tap Setting | Post Tap Setting | RPOST (Post-to-Main Cursor) |  |

|------------------|------------------|-----------------------------|--|

| 60               | 0                | 0.00                        |  |

| 59               | 1                | 0.03                        |  |

| 58               | 2                | 0.07                        |  |

| 57               | 3                | 0.10                        |  |

| 56               | 4                | 0.13                        |  |

| 55               | 5                | 0.17                        |  |

#### Table 1: Main and Post Cursor Settings (Continued)

## 15867339858

| Main Tap Setting | Post Tap Setting | RPOST (Post-to-Main Cursor) |

|------------------|------------------|-----------------------------|

| 54               | 6                | 0.20                        |

| 53               | 7                | 0.23                        |

| 52               | 8                | 0.27                        |

| 51               | 9                | 0.30                        |

| 50               | 10               | 0.33                        |

| 49               | 11               | 0.37                        |

| 48               | 12               | 0.40                        |

| 47               | 13               | 0.43                        |

| 46               | 14               | 0.47                        |

| 45               | 15               | 0.50                        |

| 44               | 16               | 0.53                        |

| 43               | 17               | 0.57                        |

| 42               | 18               | 0.60                        |

| 41               | 19 <sup>a</sup>  | 0.63                        |

| 40               | 20 <sup>a</sup>  | 0.67                        |

| 39               | 21 <sup>a</sup>  | 0.70                        |

| 38               | 22 <sup>a</sup>  | 0.73                        |

| 37               | 23 <sup>a</sup>  | 0.77                        |

a. If post 2 to 1 = 1.

#### 1.5.2 Receive Path

The receive path accepts the 10.3125 Gb/s data at the XFI (10GBASE-KR) receivers and sends the data for 10.3125 Gb/s serial transmission at the XGPHY copper interface.

#### 1.5.2.1 Limiting Amplifier

The BCM84891L differential limiting amplifier at the receiver path provides post-amplification of low-level signals between XFI (10GBASE-KR) input and the XFI (10GBASE-KR) clock recovery inputs. The differential voltage peak-to-peak swing can be between (TBD) and (TBD). The serial input has an internal  $100\Omega$  termination between the differential lines and internally biased.

#### 1.5.2.2 XFI/10GBASE-KR Clock Recovery

The XFI (10GBASE-KR) CDR generates a clock that is at the same frequency as the incoming data bit rate, 10.3125 Gb/s, at the serial data inputs, XFI\_I P/N. The clock is phase-aligned so that it samples the data at the center of the data eye pattern.

The phase relationship between the edge transitions of the data and those of the generated clock are compared by a phase/ frequency discriminator. Output pulses from the discriminator indicate the required direction of phase corrections. These pulses are smoothed by a loop filter. Frequency stability without incoming data is guaranteed by an internal reference clock that the PLL locks onto when data is lost.

#### 1.5.2.3 XFI/10GBASE-KR CDR Lock Detect

15867339858

The BCM84891L contains a lock detect circuit that monitors the 10.3125 GHz frequency of the internal VCO. The frequency of the incoming data stream must be within ±100 ppm of the 10.3125 Gb/s data stream for the lock detector to declare signal lock. CDR\_LOL goes low when the XFI (10GBASE-KR) CDR is locked to the incoming data.

#### 1.5.2.4 XFI/10GBASE-KR PMD CDR Lock to Incoming Data Detector

The BCM84891L contains a loss-of-signal (LoS) detect circuit that monitors the integrity of the serial receiver data path. A peak detector looks for a minimum amplitude swing. If the serial data input is not present, the PMD\_LOS bit in XFI (10GBASE-KR) CDR PHY Control Status Register (TBD) is set to 1.

#### 1.5.2.5 XFI/10GBASE-KR Serial Input Interface

The XFI (10GBASE-KR) serial inputs (XFI\_IP/N) have built-in AC-coupling. AC-coupling prevents voltage drops across the input devices of the BCM84891L when the input signals are sourced from a device with a higher operating voltage.

### 1.5.2.6 XFI/10GBASE-KR Equalizer

The BCM84891L includes a programmable equalizer, which provides frequency response peaking centered around the serial input signal to reduce the effects of ISI caused by long PCB traces.

#### 1.5.2.7 XFI/10GBASE-KR Deserializer

The XFI (10GBASE-KR) serial data stream is descrialized to a 64-bit word by a serial-to-parallel converter. The CDR output clocks the serial-to-parallel converter. Under normal operation, the CDR recovers the clock from the data. If data is not present, the clock is recovered from the internal reference clock. The output of this stage is sent to the RX Gearbox.

#### 1.5.2.8 XFI/10GBASE-KR Egress RX Gearbox

The RX gearbox is a buffer that receives serial data from the PMA sublayer and converts it into 66-bit blocks. The 66-block data is passed to the descrambler.

#### 1.5.2.8.1 Descrambler

The 66-bit data blocks are received from the gearbox and passed through a descrambling polynomial.

#### 1.5.2.9 64-Bit/66-Bit Synchronizer/Decoder

A Frame Synchronizer searches for valid sync-header bits to identify the boundaries of the 66-bit data frames. When valid sync-headers are obtained, lock is achieved. A descrambler processes the payload to reverse the effect of the scrambler by using the same polynomial as the link partner's TX polynomial. The receiver process decodes blocks according to IEEE 802.3ae Clause 49.

## 1.6 5G or 2.5G Rate Over XFI Interface in 10GBASE-R867339858

The BCM84891L supports 5G transfer rate over XFI interface in 10GBASE-R mode when the line side is linked at 5GBASE-T. In addition to 2500BASE-X/2500BASE-R mode, the BCM84891L supports 2.5G rate over XFI interface in 10GBASE-R when the line side is linked at 2.5GBASE-T.

The BCM84891L requires to be configured for 2.5G/5G rate over XFI mode using the command handler (see Section 1.22, MDIO Command Handler Function) after reset and before the line side auto-negotiates to link at 5GBASE-T/5GBASE-T. The BCM84891L is set to operate as 2500X/5000X mode at default.

The 5G or 2.5G transfer rate over XFI in 10GBASE-R mode is handled by the BCM84891L through data rate shaping buffer by inserting or deleting idles. The BCM84891L expects to receive packets with sufficient Inter Packet Idles from the MAC (switch/controller) for the 5G or 2.5G rate effectively transfer over the XFI interface in 10GBASE-R mode.

#### NOTE:

- AutogrEEEn mode is not supported when 5G or 2.5G rate over XFI interface in 10GBASE-R mode is used.

- 5G or 2.5G rate over XFI interface in 10GBASE-R mode is supported when KR is enabled.

- 2500X is not supported when KR mode is enabled. When KR mode is used, first enable the 2.5G rate over XFI interface in 10GBASE-R mode through the command handler.

- The maximum packet size is 15 KB for 5GBASE-T and 10 KB for 2.5GBASE-T when the MAC interface is 10G.

#### 1.7 100BASE-TX/1000BASE-T

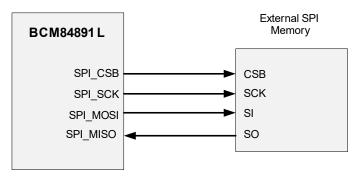

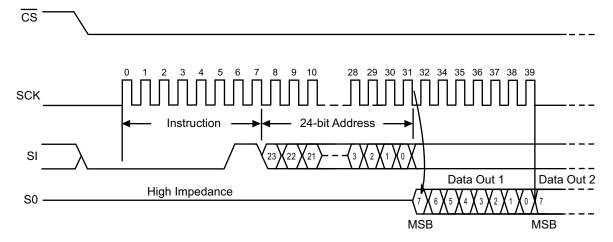

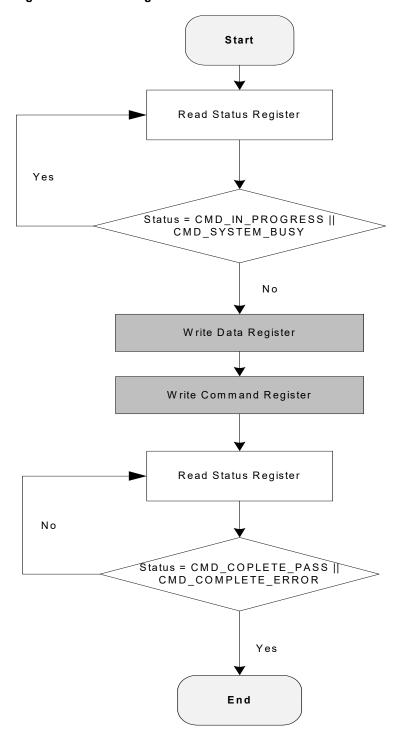

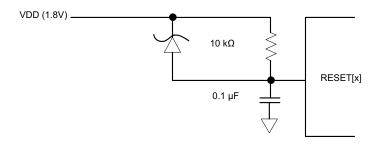

#### 1.7.1 Encoder