## 主要性能

- 最高 23 位有效分辨率

- 均方根(RMS)噪声

- 34 nV (4.17 Hz 时)

- 77 nV (16.7 Hz 时)

- 功耗: 355 µA (典型值)

- 省电模式: 最大 1 µA

- 更新速率: 4.17 Hz~940 Hz

- 3个差分输入

- 完全兼容 ADI 的 AD7793

- TSSOP-16 封装

- 接口

SPI、QSPI、MICROWIRE 和 DSP 兼容 SCLK 为施密特触发器

#### 应用场合

- 热电偶测量

- RTD 测量

- 热敏电阻测量

- 气体分析

- 工业过程控制

- 仪器仪表

- 便携式仪器仪表

- 血液分析

- 智能发射机

- 液体/气体色谱

- 6 位 DVM

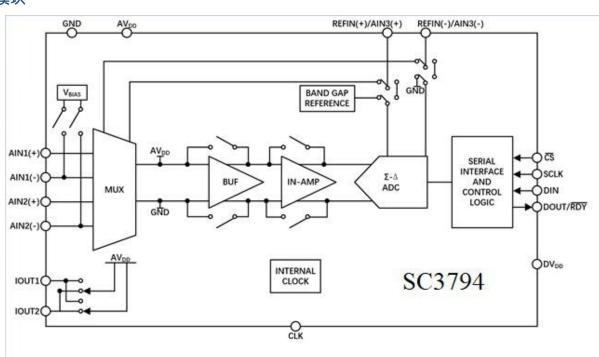

#### 功能模块

# 图 1 芯片模块示意图

## 产品概况

SC3794 为适合高精度测量应用的低功耗、低噪声、完整模拟前端,内置一个低噪声 24 位 Σ-Δ型 ADC, 其中含有 3 个差分模拟输入,还集成了片内低噪声仪表放大器,因而可直接输入小信号。当增益设置为 64、更新速率为 4.17 Hz 时,均方根(RMS)噪声为 53 nV。

器件內置一个精密低噪声、低漂移內部带隙基准电压源,而且也可采用一个外部差分基准电压。其它片內特性包括可编程激励电流源、熔断电流控制和偏置电压产生器。利用偏置电压产生器可将某一通道的共模电压设置为 AVDD/2。

SC3794 可以采用内部时钟或外部时钟工作,输出数据速率可通过软件编程设置,可在 4.17 Hz 至 940 Hz 的范围内变化。

SC3794 采用 2.7 V 至 5.25 V 电源供电,典型功耗为 355 μA,采用 16 引脚 TSSOP 封装。

## 技术规格

除非另有说明, $AV_{DD}$ =2.7V 至 5.25V、 $DV_{DD}$ =2.7V 至 5.25V、GND=0V,所有规格均相对于  $T_{MIN}$  至  $T_{MAX}$  而言。

表 1

| 参数               | SC7792/SC3794                      | 单位              | 测试条件/注释                                                                                      |  |  |

|------------------|------------------------------------|-----------------|----------------------------------------------------------------------------------------------|--|--|

| ADC 通道           |                                    |                 |                                                                                              |  |  |

| 输出更新速率           | 4.17 至 470                         | Hz,标称值          |                                                                                              |  |  |

| 无失码              | 24                                 | 位,最小值           | fadc<242Hz                                                                                   |  |  |

| N 212            | 16                                 | 位,最小值           |                                                                                              |  |  |

| 分辨率              |                                    |                 |                                                                                              |  |  |

| 输出噪声与更新速率        |                                    |                 |                                                                                              |  |  |

| 失调误差             | ±0.5                               | μV,典型值          |                                                                                              |  |  |

| 满量程误差            | ±5                                 | μV,典型值          |                                                                                              |  |  |

| 模拟输入<br>差分输入电压范围 | ±V <sub>REF</sub> /增益              | Vnom            | V <sub>REF</sub> = REFIN(+) –REFIN(-),或内部基准电<br>压,增益=1 至 128                                 |  |  |

| 共模电压(VcM)        | 0.5                                | Vmin            | V <sub>CM</sub> =(AIN(+) + AIN(-))/2,增益=4 至 128                                              |  |  |

| 基准电压             |                                    |                 |                                                                                              |  |  |

| 内部基准电压           |                                    |                 |                                                                                              |  |  |

| 内部基准电压初始精度       | 1.17±0.01%                         | V,最小值/最大值       | AV <sub>DD</sub> =4V, TA=25°C                                                                |  |  |

| 外部基准电压源          |                                    |                 |                                                                                              |  |  |

| 外部 REFIN 电压      | 2.5                                | V,标称值           | REIN=REFIN(+)-REFIN(-)                                                                       |  |  |

| 基准电压范围           | 0.1<br>AV <sub>DD</sub>            | V,最小值<br>V,最大值  | 当 V <sub>REF</sub> = AV <sub>DD</sub> 时,如果仪表放大器有效,<br>则必须将差分输入限制在 0.9×V <sub>REF</sub> /增益以内 |  |  |

| 绝对 REFIN 电压限制    | GND-30mV<br>AV <sub>DD</sub> +30mV | V,最小值<br>V,最大值  |                                                                                              |  |  |

| 激励电流源            |                                    |                 |                                                                                              |  |  |

| (IEXC1 和 IEXC2)  |                                    |                 |                                                                                              |  |  |

| 输出电流             | 10/210/1000                        | μA,标称值          |                                                                                              |  |  |

| 初始容差(25℃)        | ±3                                 | %,典型值           |                                                                                              |  |  |

| 内部/外部时钟          |                                    |                 |                                                                                              |  |  |

| 内部时钟             |                                    |                 |                                                                                              |  |  |

| 频率               | 64 ± 0.1%                          | KHz,最小值/最<br>大值 |                                                                                              |  |  |

| 占空比              | 50:50                              | %,典型值           |                                                                                              |  |  |

| 外部时钟             |                                    |                 |                                                                                              |  |  |

| 频率               | 64                                 | KHz,标称值         | 使用 2 分频功能时(位 CLK1 = CLK0 = 1),<br>可以采用 128KHz 外部时钟                                           |  |  |

| 占空比              | 45:55 to 55:45                     | %,典型值           | 适用于 64KHz 外部时钟;如果是 128KHz 时 钟,占空比要求可以稍低                                                      |  |  |

| 逻辑输入                         |                       |                |                                                                                                                    |

|------------------------------|-----------------------|----------------|--------------------------------------------------------------------------------------------------------------------|

| CS                           |                       |                |                                                                                                                    |

| V <sub>INL</sub> ,输入低电平      | 0.8<br>0.4            | V,最大值<br>V,最大值 | $DV_{DD} = 5 V$ $DV_{DD} = 3 V$                                                                                    |

| V <sub>INH</sub> ,输入高电平      | 2.0                   | V,最小值          | DVDD = 3 V  or  5 V                                                                                                |

| SCLK、CLK 和 DIN<br>(施密特触发器输入) |                       |                |                                                                                                                    |

| VT(+)                        | 1.4/2                 | V min/V max    | $DV_{DD} = 5 V$                                                                                                    |

| VT(-)                        | 0.8/1.7               | V min/V max    | $DV_{DD} = 5 V$                                                                                                    |

| VT(+) -VT(-)                 | 0.1/0.17              | V min/V max    | $DV_{DD} = 5 V$                                                                                                    |

| VT(+)                        | 0.9/2                 | V min/V max    | $DV_{DD} = 3 V$                                                                                                    |

| VT(-)                        | 0.4/1.35              | V min/V max    | $DV_{DD} = 3 V$                                                                                                    |

| VT(+) -VT(-)                 | 0.06/0.13             | V min/V max    | $DV_{DD} = 3 V$                                                                                                    |

| 输入电流                         | ±10                   | uA max         | V <sub>IN</sub> = DV <sub>DD</sub> 或 GND                                                                           |

| 输入电容                         | 10                    | pF typ         | 所有数字输入                                                                                                             |

| 逻辑输出(包括<br>CLK)              |                       |                |                                                                                                                    |

| Von,输出高电压                    | DV <sub>DD</sub> -0.6 | V min          | $DV_{DD} = 3 \text{ V}, I_{SOURCE} = 100 \mu\text{A}$                                                              |

| Vo., 输出低电压                   | 0.4                   | V max          | $DV_{DD} = 3 \text{ V},  I_{SINK} = 100  \mu\text{A}$                                                              |

| Von, 输出高电压                   | 4                     | V min          | $DV_{DD} = 5 \text{ V}, I_{SOURCE} = 200  \mu\text{A}$                                                             |

| Vol.,输出低电压 0.4               |                       | V max          | $\mathrm{DV_{DD}} = 5~\mathrm{V},~\mathrm{I_{SINK}} = 1.6~\mathrm{mA}~\mathrm{(DOUT/RDY)/800}~\mu\mathrm{A}$ (CLK) |

| 浮空态漏电流                       | ±10                   | uA max         |                                                                                                                    |

| 浮空态输出电容                      | 10                    | pF typ         |                                                                                                                    |

| 数据输出编码                       | Offset binary         |                |                                                                                                                    |

| 系统校准                         |                       |                |                                                                                                                    |

| 满量程校准限值                      | +1.05 × FS            | V max          |                                                                                                                    |

| 零电平校准限值                      | −1.05 × FS            | V min          |                                                                                                                    |

| 输入范围                         | 0.8 × FS<br>2.1 × FS  | V min<br>V max |                                                                                                                    |

| 电源要求                         |                       |                |                                                                                                                    |

| 电源电压                         |                       |                |                                                                                                                    |

| AVDD至 GND                    | 2.7/5.25              | V min/max      |                                                                                                                    |

| DV <sub>DD</sub> 至 GND       | 2.7/5.25              | V min/max      |                                                                                                                    |

| 电源电流                         |                       |                |                                                                                                                    |

| Inn电流                        | 140                   | μA max         | 典型值 120μA(AV <sub>DD</sub> = 3V), 典型值 130μA<br>(AV <sub>DD</sub> = 5V), 无缓冲模式, 外部基准电压                              |

|                              | 450                   | μA max         | 典型值 355μA(AV <sub>DD</sub> = 3V), 典型值 380μA<br>(AV <sub>DD</sub> = 5V), 增益=4 至 128, 内部基准电压                         |

| Inn(省电模式)                    | 1                     | μA max         |                                                                                                                    |

## 极限参数

| AVCC 至 GND0.3V 至 7V          |  |

|------------------------------|--|

| DVDD 至 GND0.3V 至 7V          |  |

| 模拟输入电压至 GND0.3V 至 AVDD+0.3V  |  |

| 基准输入电压至 GND0.3V 至 AVDD+0.3V  |  |

| 数字输入电压至 GND0.3V 至 DVDD+0.3V  |  |

| 数字输出电压至 GND0.3V 至 DVDD +0.3V |  |

| 工作温度范围40°C 至 105°C           |  |

| 存储温度范围65°C 至 150°C           |  |

**注意**:对以上所列的最大极限值,如果器件工作在超过此极限值的环境中,很可能会对器件造成永久性破坏。 在实际运用中,最好不要使器件工作在此极限值或超过此极限值的环境中。

本产品属于静电敏感器件。当拿取时,要采取合适的 ESD 保护措施,以免造成性能下降或功能失效。

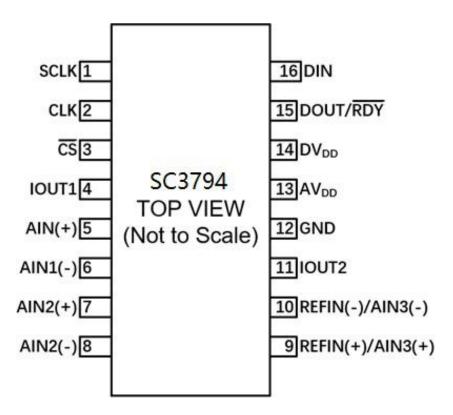

# 管脚(焊盘)配置及功能说明

图 2 管脚 (焊盘) 配置

表 6 管脚定义

| 引脚编号 | 引脚名称  | 功能                                                                                                                                                     |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | SCLK  | 串行时钟输入。用于与 ADC 进行数据传输。SCLK 具有施密特触发式输入,因而该接口适合光隔离应用。该串行时钟可以是连续式时钟,所有数据均在连续的脉冲串中传输。或者,它也可以是非连续式时钟,来往 ADC 的信息以较小的数据包形式传输。                                 |

| 2    | CLK   | 时钟输入/时钟输出引脚。通过此引脚可提供内部时钟,或者禁用内部时钟。当内部时钟被禁用后,可以采用外部时钟驱动该 ADC。这样,多个 ADC 可以由同一时钟驱动,从而执行同步转换。                                                              |

| 3    | ¯Č\$  | 片选输入引脚。这是一个低电平有效逻辑输入引脚,用于选择 ADC。<br>CS 可以用来在串行总线上具有多个器件的系统中选择 ADC,或者用<br>作帧同步信号,与器件通信。CS 可以用硬连线方式置为低电平,使得<br>ADC 能以 3 线式模式工作,通过 SCLK、DIN 和 DOUT 与器件接口。 |

| 4    | IOUT1 | 内部激励电流源的输出引脚。通过此引脚可提供内部激励电流。用户可以通过编程设置内部激励电流 源,以便将电流设置为 10μA、210μA或 1mA。可以将 IEXC1 或 IEXC2 切换至此输出。                                                      |

| 5  | AIN1(+)                     | 模拟输入引脚。AIN1(+)是差分模拟输入对 AIN1(+)/AIN1(-)的正端。                                                                                                                                                                                                                                                             |

|----|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6  | AIN1(-)                     | 模拟输入引脚。AIN1(-)是差分模拟输人对 AIN1(+)/AIN1(-)的负端。                                                                                                                                                                                                                                                             |

| 7  | AIN2(+)                     | 模拟输入引脚。AIN2(+)是差分模拟输入对 AIN2(+)/AIN2(-)的正端。                                                                                                                                                                                                                                                             |

| 8  | AIN2(-)                     | 模拟输入引脚。AIN2(-)是差分模拟输人对 AIN2(+)/AIN2(-)的负端。                                                                                                                                                                                                                                                             |

| 9  | REFIN(+)/AIN3(+)            | 模拟输入/正基准电压输入引脚。可以在正负输入之间施加一个外部基准电压。REFIN(+)可位于 AVDD 和 GND+0.1V 之间。标称基准电压 R EFIN(+)至 REFIN (+) 为 2.5V,但该器件可以采用 0.1V 至 AVDD。范围内的基准电压工作。另外,该引脚可用作 AIN3(+),即差分模拟输入对 AIN3(+)/AIN3(-)的正端。                                                                                                                    |

| 10 | REFIN(-)/AIN3(-)            | 模拟输入/负基准电压输入引脚。<br>输入可位于 GND 与 AVDD0.1V 之间。除此<br>外,该引脚还可用作 AIN3(-),即差分模拟输入对 AIN3(+)/ AIN3(-                                                                                                                                                                                                            |

| 11 | IOUT2                       | 内部激励电流源的输出引脚。通过此引脚可提供内部激励电流源。用户可以通过编程设置内部激励电 流源,以便将电流设置为 10μA、210 μA 或 1mA。可以将 IEXC1 或 IEXC2 切换至此输出。                                                                                                                                                                                                   |

| 12 | GND                         | 接地基准点。                                                                                                                                                                                                                                                                                                 |

| 13 | $\mathrm{AV}_{\mathrm{DD}}$ | 电源电压(2.7V 至 5.25V)。                                                                                                                                                                                                                                                                                    |

| 14 | $\mathrm{DV}_{\mathrm{DD}}$ | 数字接口电源引脚。串行接口引脚的逻辑电平与该电源有关,在 2.7V 与 5.25V 之间。DV <sub>DD</sub> 引脚电压与 AV <sub>DD</sub> 引脚电压无关;因此,AV <sub>DD</sub> =5 V、DV <sub>DD</sub> =3V,反之亦然。                                                                                                                                                        |

| 15 | DOUT/ <b>B</b> Y            | 串行数据输出/数据就绪输出引脚。DOUT/RDY 具有双重作用。它可以用作串行数据输出引脚,以访问 ADC 的输出移位寄存器。输出移位寄存器可以含有来自任一片内数据寄存器或控制寄存器的数据。此外,DOUT/RDY 可以用作数据就绪引脚。当引脚的电平为低时,表示转换己完成。转换完成后,如果数 据未被读取,该引脚将在下次更新之前变为高电平。<br>DOUT/RDY 下降沿可以用作处理器的中断,表示存在可用数据。采用外部串行时钟时,可以利用 DOUT/RDY 引脚读取数据。CS 为低电平时,数据/控制字信息在 SCLK 下降沿被置于 DOUT/RDY 引脚上,且在 SCLK 上升沿有效。 |

| 16 | DIN                         | 串行数据输入。该串行数据输入用于 ADC 的输入移位寄存器。该移位寄存器中的数据传输至 ADC 内的控制寄存器;通信寄存器的寄存器选择位可以识别恰当的寄存器。                                                                                                                                                                                                                        |

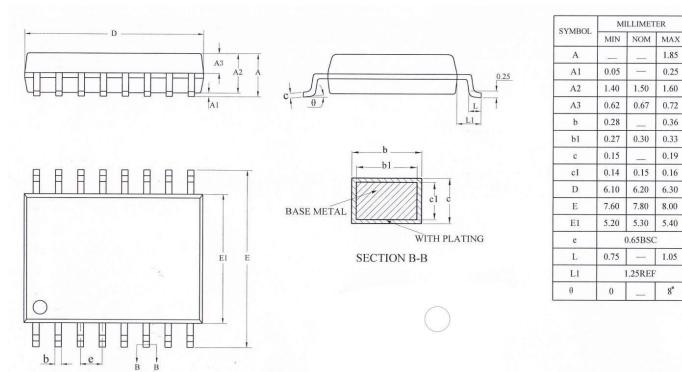

#### 外形尺寸

图 316脚 TSSOP 封装尺寸图

MILLIMETER

1.50

0.67

0.15

6.20

7.80

0.65BSC

1.25REF

1.85

1.60 0.72

0.36

0.33 0.19

0.16

6.30

8.00

5.40

1.05

8°

表 7.输出均方根噪声(uV)与增益和输出更新速率的关系(采用外部基准电压源)

| 更新速率<br>(Hz) | 增益=1 | 增益=2 | 增益=4 | 增益=8 | 增益=16 | 增益=32 | 增益=64 | 增益=128 |

|--------------|------|------|------|------|-------|-------|-------|--------|

| 4.17         | 0.83 | 0.54 | 0.29 | 0.16 | 0.10  | 0.069 | 0.046 | 0.034  |

| 8.33         | 1.00 | 0.74 | 0.38 | 0.23 | 0.14  | 0.098 | 0.063 | 0.046  |

| 16.7         | 1.53 | 1.18 | 0.66 | 0.36 | 0.24  | 0.16  | 0.10  | 0.077  |

| 33.2         | 2.41 | 1.94 | 1.00 | 0.62 | 0.39  | 0.25  | 0.17  | 0.12   |

## 表 8.输出均方根噪声(uV)与增益和输出更新速率的关系(采用内部基准电压源)

| 更新速率<br>(Hz) | 增益=1 | 增益=2 | 增益=4 | 增益=8 | 增益=16 | 增益=32 | 增益=64 | 增益=128 |

|--------------|------|------|------|------|-------|-------|-------|--------|

| 4.17         | 0.69 | 0.55 | 0.27 | 0.16 | 0.10  | 0.073 | 0.052 | 0.039  |

| 8.33         | 1.10 | 0.81 | 0.42 | 0.24 | 0.15  | 0.10  | 0.075 | 0.057  |

| 16.7         | 1.68 | 1.25 | 0.68 | 0.41 | 0.26  | 0.17  | 0.11  | 0.087  |

| 33.2         | 2.67 | 2.01 | 1.18 | 0.67 | 0.41  | 0.27  | 0.18  | 0.14   |

| 470          | 8.89 | 6.05 | 3.39 | 1.88 | 1.21  | 0.90  | 0.68  | 0.58   |

# 典型噪声图 内部基准电压,增益=16,更新速率=16.7

图 4 SC3794 的典型噪声图

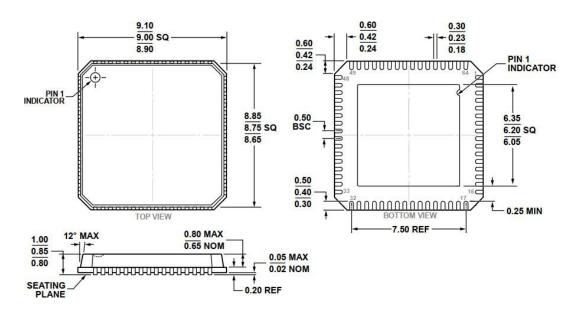

图 14 64 脚 QFN 封装尺寸图

上海芯炽集成电路技术有限公司 国芯思辰 (深圳) 科技有限公司

深圳公司:深圳市福田区石厦街新天世纪商务中心A座1513室

公司网址:www.zhongke-ic.com

联系电话:0755-82565229