### 16Mega x 16 Synchronous DRAM (SDRAM)

(Rev 1.1, Apr., 2007)

### **Features**

- Fast access time from clock: 5/5.4 ns

- Fast clock rate: 166/143 MHz

- Fully synchronous operation

- Internal pipelined architecture

- 4M word x 16-bit x 4-bank

- Programmable Mode registers

- CAS# Latency: 2, or 3

- Burst Length: 1, 2, 4, 8, or full page

- Burst Type: interleaved or linear burst

- Burst stop function

- Auto Refresh and Self Refresh

- 8192 refresh cycles/64ms

- CKE power down mode

- Single +3.3V power supply

- Interface: LVTTL

- 54-pin 400 mil plastic TSOP II Lead-free package

### **Overview**

The EM63A165 SDRAM is a high-speed CMOS synchronous DRAM containing 256 Mbits. It is internally configured as 4 Banks of 2M word x 16 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of a BankActivate command which is then followed by a Read or Write command.

The EM63A165 provides for programmable Read or Write burst lengths of 1, 2, 4, 8, or full page, with a burst termination option. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst sequence. The refresh functions, either Auto or Self Refresh are easy to use.

By having a programmable mode register, the system can choose the most suitable modes to maximize its performance. These devices are well suited for applications requiring high memory bandwidth and particularly well suited to high performance PC applications.

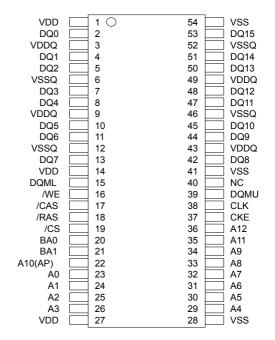

### Pin Assignment (Top View)

### **Key Specifications**

|                  | EM63A165                   | - 6/7    |

|------------------|----------------------------|----------|

| t <sub>CK3</sub> | Clock Cycle time(min.)     | 6/7 ns   |

| t <sub>AC3</sub> | Access time from CLK(max.) | 5/5.4 ns |

| t <sub>RAS</sub> | Row Active time(min.)      | 42/45 ns |

| t <sub>RC</sub>  | Row Cycle time(min.)       | 60/63 ns |

### **Ordering Information**

| Part Number   | Frequency | Package |  |  |

|---------------|-----------|---------|--|--|

| EM63A165TS-6G | 166MHz    | TSOP II |  |  |

| EM63A165TS-7G | 143MHz    | TSOP II |  |  |

## Etron Technology, Inc.

No. 6, Technology Rd. V, Science-Based Industrial Park, Hsinchu, Taiwan 30077, R.O.C. TEL: (886)-3-5782345 FAX: (886)-3-5778671

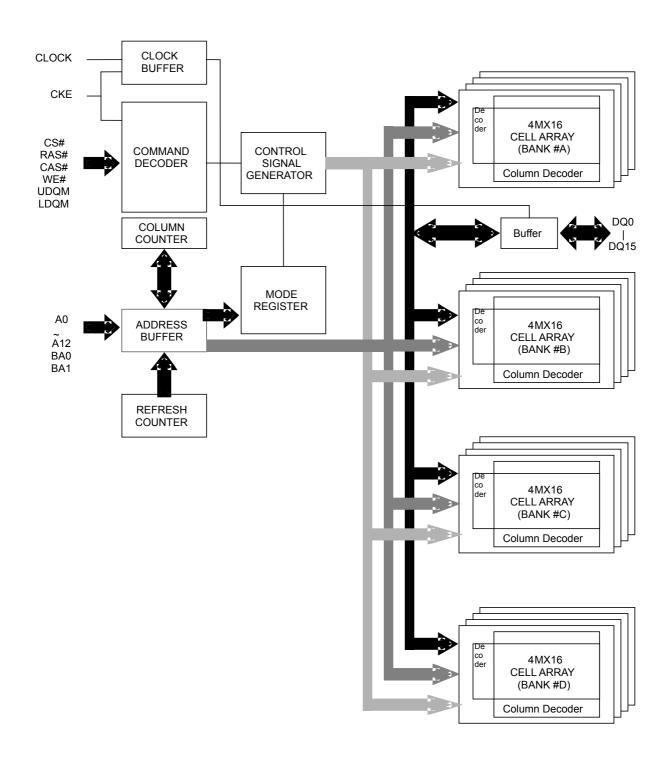

### **Block Diagram**

## **Pin Descriptions**

Table 1. Pin Details of EM63A165

| Symbol  | Туре  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Description                                                                                                   |                                                                                                                                   |  |  |  |  |  |  |

|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| CLK     | Input |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | K. ČLK also increments the                                                                                    | I input signals are sampled internal burst counter and                                                                            |  |  |  |  |  |  |

| CKE     | Input | Clock Enable: CKE activates(HIGH) and deactivates(LOW) the CLK signal. If CKE goes low synchronously with clock(set-up and hold time same as other inputs), the internal clock is suspended from the next clock cycle and the state of output and burst address is frozen as long as the CKE remains low. When all banks are in the idle state, deactivating the clock controls the entry to the Power Down and Self Refresh modes. CKE is synchronous except after the device enters Power Down and Self Refresh modes, where CKE becomes asynchronous until exiting the same mode. The input buffers, including CLK, are disabled during Power Down and Self Refresh modes, providing low standby power. |                                                                                                               |                                                                                                                                   |  |  |  |  |  |  |

| BA0,BA1 | Input | Bank Select: BA0,BA1 inp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | out select the bank for opera                                                                                 | ation.                                                                                                                            |  |  |  |  |  |  |

|         |       | BA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BA0                                                                                                           | Select Bank                                                                                                                       |  |  |  |  |  |  |

|         |       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0                                                                                                             | BANK #A                                                                                                                           |  |  |  |  |  |  |

|         |       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                             | BANK #B                                                                                                                           |  |  |  |  |  |  |

|         |       | 1 0 BANK #C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |                                                                                                                                   |  |  |  |  |  |  |

|         |       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                             | BANK #D                                                                                                                           |  |  |  |  |  |  |

| A0-A12  | Input | address A0-A11) and Readefining Auto Precharge) respective bank. During a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ad/Write command (column<br>to select one location out<br>Precharge command, A10<br>arged (A10 = HIGH). The a | ankActivate command (rown address A0-A8 with A10 of the 4M available in the is sampled to determine if ddress inputs also provide |  |  |  |  |  |  |

| CS#     | Input | command decoder. All com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nmands are masked when (<br>nk selection on systems                                                           | ables (sampled HIGH) the CS# is sampled HIGH. CS# with multiple banks. It is                                                      |  |  |  |  |  |  |

| RAS#    | Input | Row Address Strobe: The RAS# signal defines the operation commands in conjunction with the CAS# and WE# signals and is latched at the positive edges of CLK. When RAS# and CS# are asserted "LOW" and CAS# is asserted "HIGH," either the BankActivate command or the Precharge command is selected by the WE# signal. When the WE# is asserted "HIGH," the BankActivate command is selected and the bank designated by BS is turned on to the active state. When the WE# is asserted "LOW," the Precharge command is selected and the bank designated by BS is switched to the idle state after the precharge operation.                                                                                  |                                                                                                               |                                                                                                                                   |  |  |  |  |  |  |

| CAS#    | Input | conjunction with the RAS# of CLK. When RAS# is he                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | and WE# signals and is la<br>eld "HIGH" and CS# is as<br>ting CAS# "LOW." Then, th                            | the operation commands in<br>tched at the positive edges<br>serted "LOW," the column<br>te Read or Write command                  |  |  |  |  |  |  |

# **EtronTech**

# 15867339858

# EM63A165

| WE#             | Input             | <b>Write Enable:</b> The WE# signal defines the operation commands in conjunction with the RAS# and CAS# signals and is latched at the positive edges of CLK. The WE# input is used to select the BankActivate or Precharge command and Read or Write command. |

|-----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDQM,<br>UDQM   | Input             | Data Input/Output Mask: Controls output buffers in read mode and masks Input data in write mode.                                                                                                                                                               |

| DQ0-DQ15        | Input /<br>Output | <b>Data I/O:</b> The DQ0-15 input and output data are synchronized with the positive edges of CLK. The I/Os are maskable during Reads and Writes.                                                                                                              |

| NC/RFU          | -                 | No Connect: These pins should be left unconnected.                                                                                                                                                                                                             |

| VDDQ            | Supply            | <b>DQ Power:</b> Provide isolated power to DQs for improved noise immunity. ( $3.3V\pm0.3V$ )                                                                                                                                                                  |

| Vssq            | Supply            | <b>DQ Ground:</b> Provide isolated ground to DQs for improved noise immunity. ( 0 V )                                                                                                                                                                          |

| V <sub>DD</sub> | Supply            | Power Supply: +3.3V ± 0.3V                                                                                                                                                                                                                                     |

| Vss             | Supply            | Ground                                                                                                                                                                                                                                                         |

### **Operation Mode**

Fully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 2 shows the truth table for the operation commands.

Table 2. Truth Table (Note (1), (2))

| Command                  | State                 | CKE <sub>n-1</sub> | CKEn | DQM | BA0,1 | A10   | A0-9,12              | CS# | RAS# | CAS# | WE# |

|--------------------------|-----------------------|--------------------|------|-----|-------|-------|----------------------|-----|------|------|-----|

| BankActivate             | Idle <sup>(3)</sup>   | Н                  | Х    | Х   | V     | Row   | address              | L   | L    | Н    | Η   |

| BankPrecharge            | Any                   | Н                  | Х    | Х   | V     | L     | Х                    | L   | L    | Н    | L   |

| PrechargeAll             | Any                   | Н                  | Х    | Х   | Х     | Н     | Х                    | L   | L    | Н    | L   |

| Write                    | Active <sup>(3)</sup> | Н                  | Х    | Х   | V     | L     | Column               | L   | Н    | L    | L   |

| Write and AutoPrecharge  | Active <sup>(3)</sup> | Н                  | Х    | Х   | V     | Н     | address<br>(A0 ~ A8) | L   | Н    | L    | L   |

| Read                     | Active <sup>(3)</sup> | Н                  | Х    | Х   | V     | L     | Column               | L   | Н    | L    | Н   |

| Read and Autoprecharge   | Active <sup>(3)</sup> | Н                  | Х    | Х   | V     | Н     | address<br>(A0 ~ A8) | L   | Н    | L    | Н   |

| Mode Register Set        | Idle                  | Н                  | Х    | Х   |       | OP co | ode                  | L   | L    | L    | L   |

| No-Operation             | Any                   | Н                  | Х    | Х   | Х     | Х     | Х                    | L   | Н    | Н    | Н   |

| Burst Stop               | Active(4)             | Н                  | Х    | Х   | Х     | Х     | Х                    | L   | Н    | Н    | L   |

| Device Deselect          | Any                   | Н                  | Х    | Х   | Х     | Х     | Х                    | Н   | Х    | Х    | Х   |

| AutoRefresh              | Idle                  | Н                  | Н    | Х   | Х     | Х     | Х                    | L   | L    | L    | Н   |

| SelfRefresh Entry        | Idle                  | Н                  | L    | Х   | Х     | Х     | Х                    | L   | L    | L    | Н   |

| SelfRefresh Exit         | Idle                  |                    | Н    | Х   | Х     | Х     | Х                    | Н   | Х    | Х    | Х   |

|                          | (SelfRefresh)         | L                  |      | ^   | ^     | ^     | ^                    | L   | Н    | Н    | Н   |

| Clock Suspend Mode Entry | Active                | Н                  | L    | Х   | Х     | Х     | Х                    | Х   | Х    | Х    | Х   |

| Power Down Mode Entry    | Any <sup>(5)</sup>    |                    | ,    | V   | V     | V     | V                    | Н   | Х    | Х    | Х   |

|                          |                       | Н                  | L    | X   | X     | Х     | X                    | L   | Н    | Н    | Н   |

| Clock Suspend Mode Exit  | Active                | L                  | Н    | Х   | Х     | Х     | Х                    | Х   | Х    | Х    | Х   |

| Power Down Mode Exit     | Any                   | L                  | Н    | Х   | Х     | Х     | Х                    | Н   | Х    | Х    | Х   |

|                          | (PowerDown)           |                    |      |     |       |       |                      | L   | Н    | Н    | Н   |

| Data Write/Output Enable | Active                | Н                  | Х    | L   | Х     | Х     | Х                    | Х   | Х    | Х    | Х   |

| Data Mask/Output Disable | Active                | Н                  | Х    | Н   | Х     | Х     | Х                    | Х   | Х    | Х    | Х   |

Note: 1. V=Valid X=Don't Care L=Low level H=High level

2. CKE<sub>n</sub> signal is input level when commands are provided.

CKE<sub>n-1</sub> signal is input level one clock cycle before the commands are provided.

- 3. These are states of bank designated by BS signal.

- 4. Device state is 1, 2, 4, 8, and full page burst operation.

- 5. Power Down Mode can not enter in the burst operation.

When this command is asserted in the burst cycle, device state is clock suspend mode.

### **Commands**

#### 1 BankActivate

(RAS# = "L", CAS# = "H", WE# = "H", BAs = Bank, A0-A12 = Row Address)

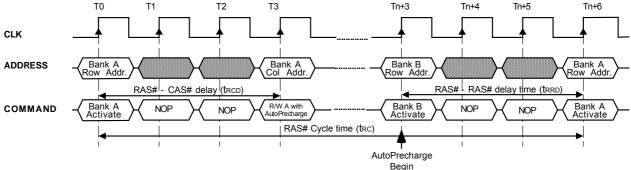

The BankActivate command activates the idle bank designated by the BA0,1 signals. By latching the row address on A0 to A12 at the time of this command, the selected row access is initiated. The read or write operation in the same bank can occur after a time delay of tRCD(min.) from the time of bank activation. A subsequent BankActivate command to a different row in the same bank can only be issued after the previous active row has been precharged (refer to the following figure). The minimum time interval between successive BankActivate commands to the same bank is defined by tRC(min.). The SDRAM has four internal banks on the same chip and shares part of the internal circuitry to reduce chip area; therefore it restricts the back-to-back activation of the four banks. tRRD(min.) specifies the minimum time required between activating different banks. After this command is used, the Write command and the Block Write command perform the no mask write operation.

### : "H" or "L"

### BankActivate Command Cycle (Burst Length = n, CAS# Latency = 3)

### 2 BankPrecharge command

(RAS# = "L", CAS# = "H", WE# = "L", BAs = Bank, A10 = "L", A0-A9, A11 and A12 = Don't care)

The BankPrecharge command precharges the bank disignated by BA signal. The precharged bank is switched from the active state to the idle state. This command can be asserted anytime after tras(min.) is satisfied from the BankActivate command in the desired bank. The maximum time any bank can be active is specified by tras(max.). Therefore, the precharge function must be performed in any active bank within tras(max.). At the end of precharge, the precharged bank is still in the idle state and is ready to be activated again.

### 3 PrechargeAll command

(RAS# = "L", CAS# = "H", WE# = "L", BAs = Don't care, A10 = "H", A0-A9, A11 and A12 = Don't care)

The PrechargeAll command precharges all banks simultaneously and can be issued even if all banks are not in the active state. All banks are then switched to the idle state.

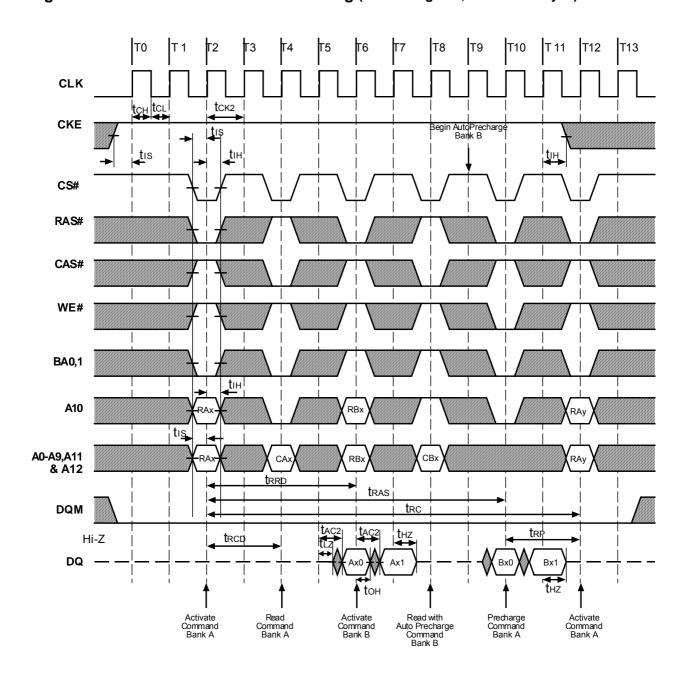

### 4 Read command

(RAS# = "H", CAS# = "L", WE# = "H", BAs = Bank, A10 = "L", A0-A8 = Column Address)

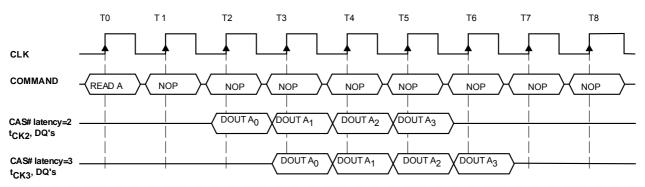

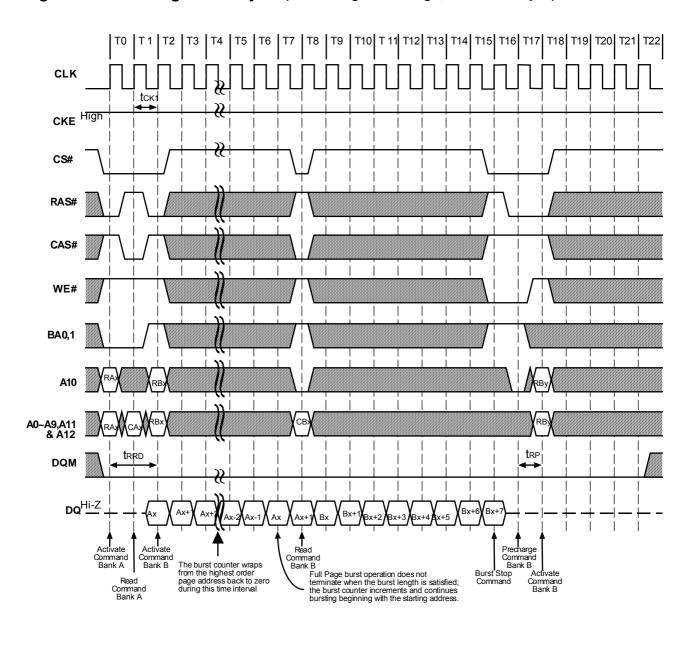

The Read command is used to read a burst of data on consecutive clock cycles from an active row in an active bank. The bank must be active for at least tRCD(min.) before the Read command is issued. During read bursts, the valid data-out element from the starting column address will be available following the CAS# latency after the issue of the Read command. Each subsequent data-out element will be valid by the next positive clock edge (refer to the following figure). The DQs go into high-impedance at the end of the burst unless other command is initiated. The burst length, burst sequence, and CAS# latency are determined by the mode register, which is already programmed. A full-page burst will continue until terminated (at the end of the page it will wrap to column 0 and continue).

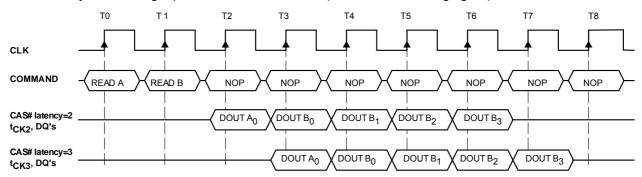

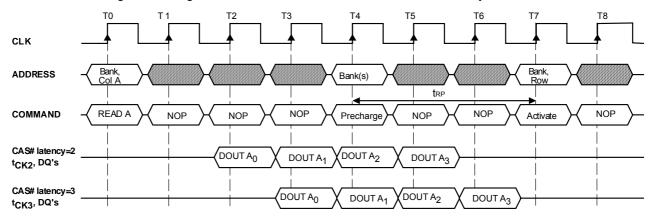

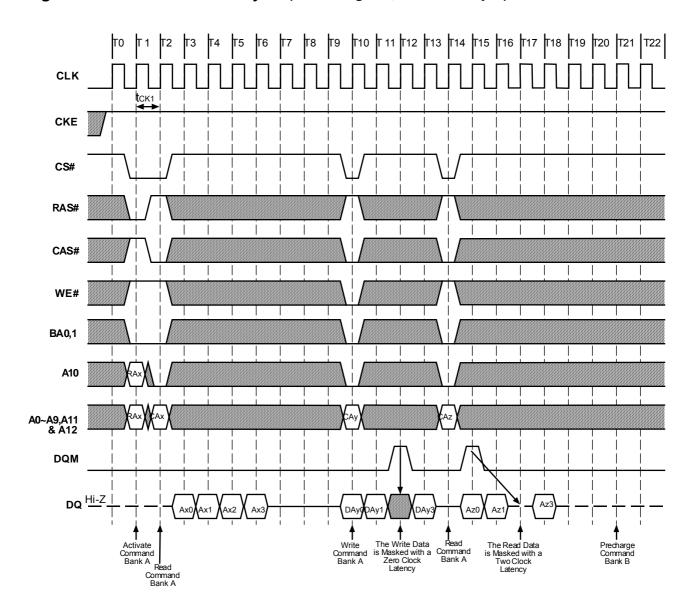

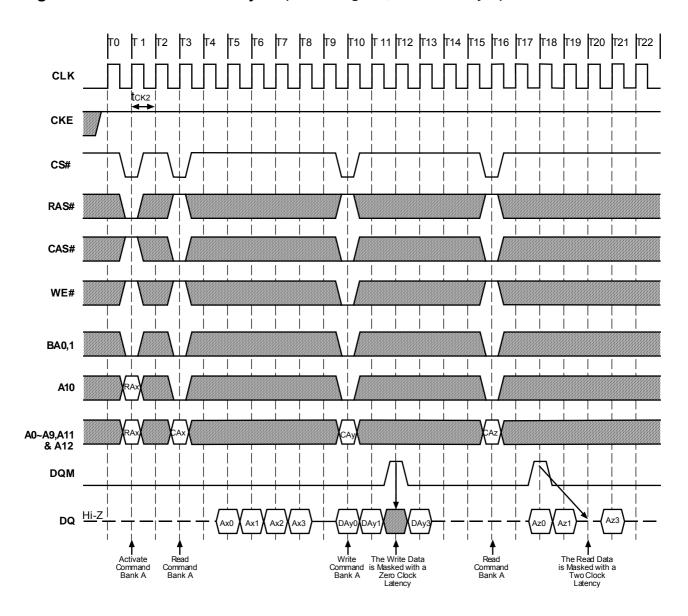

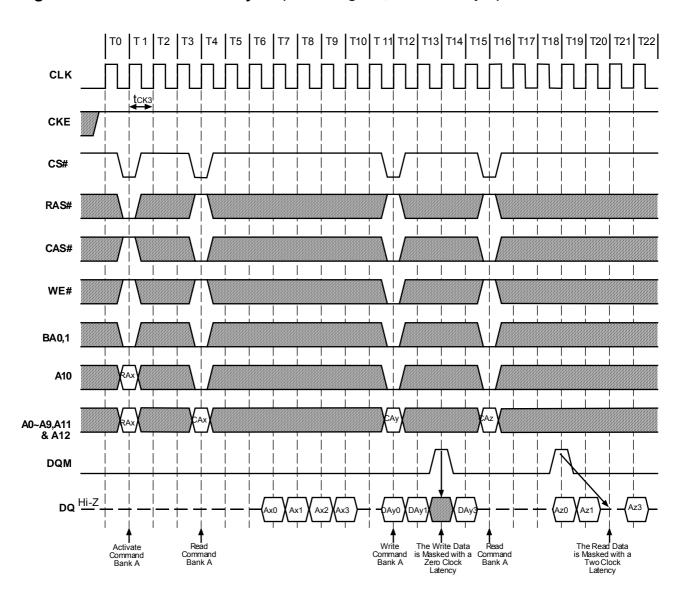

Burst Read Operation(Burst Length = 4, CAS# Latency = 2, 3)

The read data appears on the DQs subject to the values on the DQM inputs two clocks earlier (i.e. DQM latency is two clocks for output buffers). A read burst without the auto precharge function may be interrupted by a subsequent Read or Write command to the same bank or the other active bank before the end of the burst length. It may be interrupted by a BankPrecharge/ PrechargeAll command to the same bank too. The interrupt coming from the Read command can occur on any clock cycle following a previous Read command (refer to the following figure).

Read Interrupted by a Read (Burst Length = 4, CAS# Latency = 2, 3)

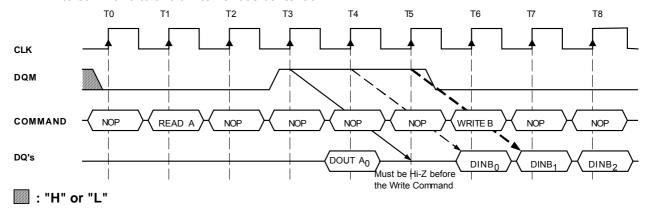

The DQM inputs are used to avoid I/O contention on the DQ pins when the interrupt comes from a Write command. The DQMs must be asserted (HIGH) at least two clocks prior to the Write command to suppress data-out on the DQ pins. To guarantee the DQ pins against I/O contention, a single cycle with high-impedance on the DQ pins must occur between the last read data and the Write command (refer to the following three figures). If the data output of the burst read occurs at the second clock of the burst write, the DQMs must be asserted (HIGH) at least one clock prior to the Write command to avoid internal bus contention.

Read to Write Interval (Burst Length ≥ 4, CAS# Latency = 3)

Read to Write Interval (Burst Length ≥ 4, CAS# Latency = 2)

Read to Write Interval (Burst Length ≥ 4, CAS# Latency = 2)

A read burst without the auto precharge function may be interrupted by a BankPrecharge/ PrechargeAll command to the same bank. The following figure shows the optimum time that BankPrecharge/ PrechargeAll command is issued in different CAS# latency.

Read to Precharge (CAS# Latency = 2, 3)

5 Read and AutoPrecharge command (RAS# = "H", CAS# = "L", WE# = "H", BAs = Bank, A10 = "H", A0-A8 = Column Address)

The Read and AutoPrecharge command automatically performs the precharge operation after the read operation. Once this command is given, any subsequent command cannot occur within a time delay of {tRP(min.) + burst length}. At full-page burst, only the read operation is performed in this command and the auto precharge function is ignored.

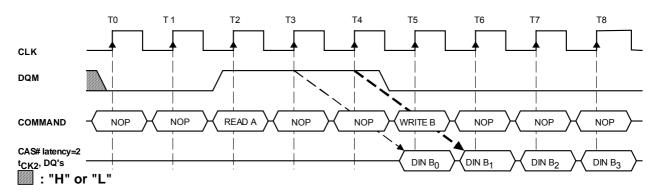

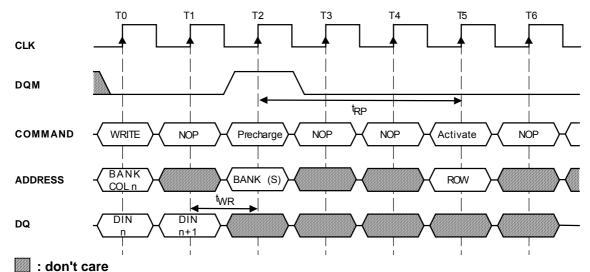

#### 6 Write command

(RAS# = "H", CAS# = "L", WE# = "L", BAs = Bank, A10 = "L", A0-A8 = Column Address)

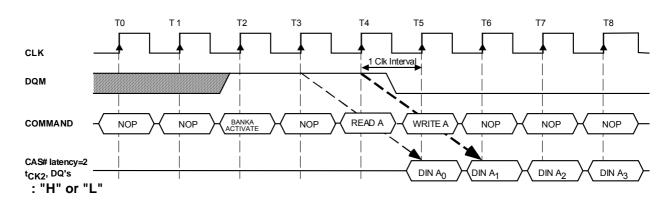

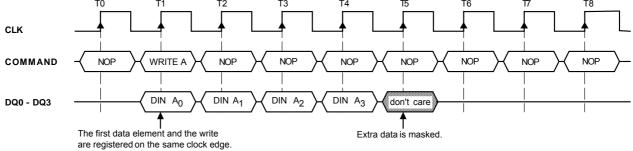

The Write command is used to write a burst of data on consecutive clock cycles from an active row in an active bank. The bank must be active for at least trcp(min.) before the Write command is issued. During write bursts, the first valid data-in element will be registered coincident with the Write command. Subsequent data elements will be registered on each successive positive clock edge (refer to the following figure). The DQs remain with high-impedance at the end of the burst unless another command is initiated. The burst length and burst sequence are determined by the mode register, which is already programmed. A full-page burst will continue until terminated (at the end of the page it will wrap to column 0 and continue).

Burst Write Operation (Burst Length = 4, CAS# Latency = 1, 2, 3)

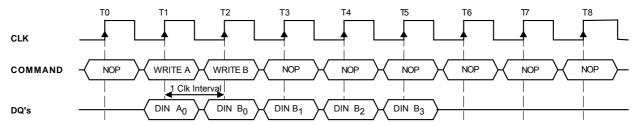

A write burst without the auto precharge function may be interrupted by a subsequent Write, BankPrecharge/PrechargeAll, or Read command before the end of the burst length. An interrupt coming from Write command can occur on any clock cycle following the previous Write command (refer to the following figure).

### Write Interrupted by a Write (Burst Length = 4, CAS# Latency = 1, 2, 3)

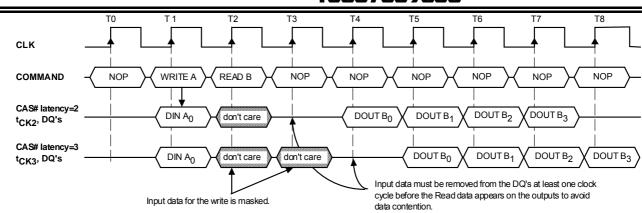

The Read command that interrupts a write burst without auto precharge function should be issued one cycle after the clock edge in which the last data-in element is registered. In order to avoid data contention, input data must be removed from the DQs at least one clock cycle before the first read data appears on the outputs (refer to the following figure). Once the Read command is registered, the data inputs will be ignored and writes will not be executed.

Write Interrupted by a Read (Burst Length = 4, CAS# Latency = 2, 3)

The BankPrecharge/PrechargeAll command that interrupts a write burst without the auto precharge function should be issued m cycles after the clock edge in which the last data-in element is registered, where m equals twr/tck rounded up to the next whole number. In addition, the DQM signals must be used to mask input data, starting with the clock edge following the last data-in element and ending with the clock edge on which the BankPrecharge/PrechargeAll command is entered (refer to the following figure).

**Note:** The DQMs can remain low in this example if the length of the write burst is 1 or 2.

### Write to Precharge

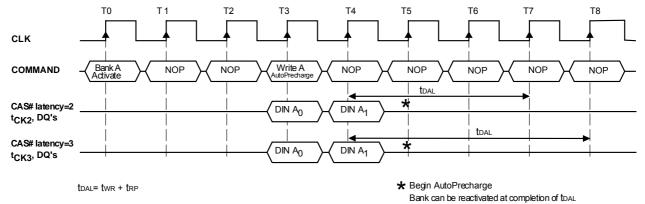

7 Write and AutoPrecharge command (RAS# = "H", CAS# = "L", WE# = "L", BAs = Bank, A10 = "H", A0-A8 = Column Address)

The Write and AutoPrecharge command performs the precharge operation automatically after the write operation. Once this command is given, any subsequent command can not occur within a time delay of {(burst length -1) +  $t_{WR}$  +  $t_{RP}$ (min.)}. At full-page burst, only the write operation is performed in this command and the auto precharge function is ignored.

### Burst Write with Auto-Precharge (Burst Length = 2, CAS# Latency = 2, 3)

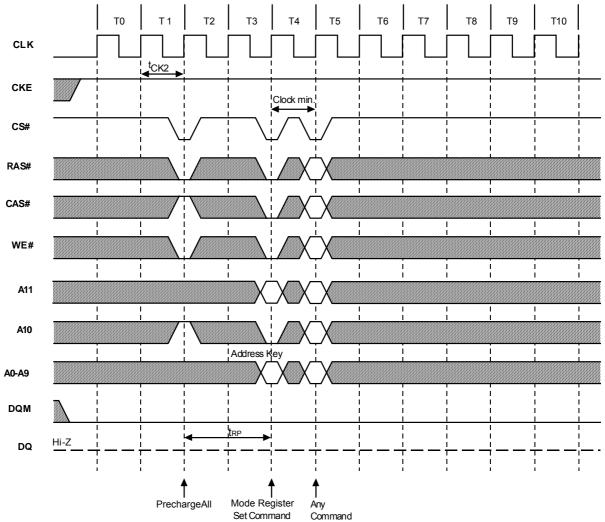

8 Mode Register Set command (RAS# = "L", CAS# = "L", WE# = "L", A0-A12 = Register Data)

The mode register stores the data for controlling the various operating modes of SDRAM. The Mode Register Set command programs the values of CAS# latency, Addressing Mode and Burst Length in the Mode register to make SDRAM useful for a variety of different applications. The default values of the Mode Register after power-up are undefined; therefore this command must be issued at the power-up sequence. The state of pins A0~A9 and A11 in the same cycle is the data written to the mode register. One clock cycle is required to complete the write in the mode register (refer to the following figure). The contents of the mode register can be changed using the same command and the clock cycle requirements during operation as long as all banks are in the idle state.

Mode Register Set Cycle (CAS# Latency = 2, 3)

The mode register is divided into various fields depending on functionality.

| Address  | BS0,1 | A12~10 | A9  | A8 | A7 | A6          | A5 | A4 | A3 | A2       | A1  | A0 |

|----------|-------|--------|-----|----|----|-------------|----|----|----|----------|-----|----|

| Function | RFU*  | RFU*   | WBL | 0  | 0  | CAS Latency |    | ВТ | Bu | rst Lenç | gth |    |

<sup>\*</sup>Note: RFU (Reserved for future use) should stay "0" during MRS cycle.

### • Burst Length Field (A2~A0)

This field specifies the data length of column access using the A2~A0 pins and selects the Burst Length to be 2, 4, 8, or full page.

| A2 | A1 | A0 | Burst Length |

|----|----|----|--------------|

| 0  | 0  | 0  | 1            |

| 0  | 0  | 1  | 2            |

| 0  | 1  | 0  | 4            |

| 0  | 1  | 1  | 8            |

| 1  | 0  | 0  | Reserved     |

| 1  | 0  | 1  | Reserved     |

| 1  | 1  | 0  | Reserved     |

| 1  | 1  | 1  | Full Page    |

Full Page Length: 512

### Burst Type Field (A3)

The Burst Type can be one of two modes, Interleave Mode or Sequential Mode.

| A3 | Burst Type |

|----|------------|

| 0  | Sequential |

| 1  | Interleave |

### --- Addressing Sequence of Sequential Mode

An internal column address is performed by increasing the address from the column address which is input to the device. The internal column address is varied by the Burst Length as shown in the following table. When the value of column address, (n + m), in the table is larger than 255, only the least significant 8 bits are effective.

| Data n         | 0 | 1                                                                | 2   | 3   | 4   | 5   | 6   | 7   | - | 255   | 256 | 257 | - |

|----------------|---|------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|---|-------|-----|-----|---|

| Column Address | n | n+1                                                              | n+2 | n+3 | n+4 | n+5 | n+6 | n+7 | - | n+255 | n   | n+1 | - |

| Burst Length   |   | words:                                                           |     |     |     |     |     |     |   |       |     |     |   |

|                |   | 8 words: Full Page: Column address is repeated until terminated. |     |     |     |     |     |     |   |       |     |     |   |

#### --- Addressing Sequence of Interleave Mode

A column access is started in the input column address and is performed by inverting the address bits in the sequence shown in the following table.

| Data n |           |    |    |    | Burst Length |    |     |     |         |         |

|--------|-----------|----|----|----|--------------|----|-----|-----|---------|---------|

| Data 0 | A8<br>A0  | A7 | A6 | A5 | A4           | A3 | A2  | A1  |         |         |

| Data 1 | A8<br>A0# | A7 | A6 | A5 | A4           | A3 | A2  | A1  | 4 words |         |

| Data 2 | A8<br>A0  | A7 | A6 | A5 | A4           | A3 | A2  | A1# |         |         |

| Data 3 | A8<br>A0# | A7 | A6 | A5 | A4           | A3 | A2  | A1# |         | 8 words |

| Data 4 | A8<br>A0  | A7 | A6 | A5 | A4           | A3 | A2# | A1  |         |         |

# **EtronTech**

# 15867339858

EM63A165

| Data 5 | A8<br>A0# | A7 | A6 | A5 | A4 | A3 | A2# | A1  |  |

|--------|-----------|----|----|----|----|----|-----|-----|--|

| Data 6 | A8<br>A0  | A7 | A6 | A5 | A4 | A3 | A2# | A1# |  |

| Data 7 | A8<br>A0# | A7 | A6 | A5 | A4 | A3 | A2# | A1# |  |

### CAS# Latency Field (A6~A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first read data. The minimum whole value of CAS# Latency depends on the frequency of CLK. The minimum whole value satisfying the following formula must be programmed into this field.

tcac(min) ≤ CAS# Latency X tck

| A6 | A5 | A4 | CAS# Latency |

|----|----|----|--------------|

| 0  | 0  | 0  | Reserved     |

| 0  | 0  | 1  | Reserved     |

| 0  | 1  | 0  | 2 clocks     |

| 0  | 1  | 1  | 3 clocks     |

| 1  | X  | X  | Reserved     |

### • Write Burst Length (A9)

This bit is used to select the burst write length.

| A9 | Write Burst Length |  |  |

|----|--------------------|--|--|

| 0  | Burst              |  |  |

| 1  | Single Bit         |  |  |

### 9 No-Operation command

(RAS# = "H", CAS# = "H", WE# = "H")

The No-Operation command is used to perform a NOP to the SDRAM which is selected (CS# is Low). This prevents unwanted commands from being registered during idle or wait states.

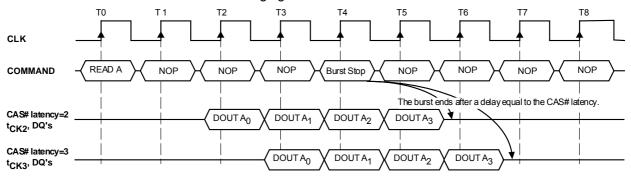

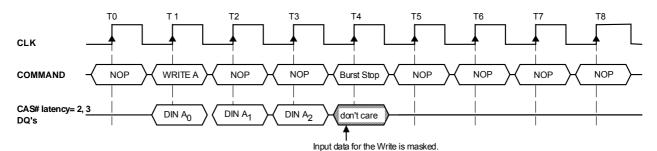

### 10 Burst Stop command

(RAS# = "H", CAS# = "H", WE# = "L")

The Burst Stop command is used to terminate either fixed-length or full-page bursts. This command is only effective in a read/write burst without the auto precharge function. The terminated read burst ends after a delay equal to the CAS# latency (refer to the following figure). The termination of a write burst is shown in the following figure.

Termination of a Burst Read Operation (Burst Length > 4, CAS# Latency = 2, 3)

Termination of a Burst Write Operation (Burst Length = X, CAS# Latency = 1, 2, 3)

### 11 Device Deselect command (CS# = "H")

The Device Deselect command disables the command decoder so that the RAS#, CAS#, WE# and Address inputs are ignored, regardless of whether the CLK is enabled. This command is similar to the No Operation command.

#### 12 AutoRefresh command

(RAS# = "L", CAS# = "L", WE# = "H", CKE = "H", A0-A12 = Don't care)

The AutoRefresh command is used during normal operation of the SDRAM and is analogous to CAS#-before-RAS# (CBR) Refresh in conventional DRAMs. This command is non-persistent, so it must be issued each time a refresh is required. The addressing is generated by the internal refresh controller. This makes the address bits a "don't care" during an AutoRefresh command. The internal refresh counter increments automatically on every auto refresh cycle to all of the rows. The refresh operation must be performed 8192 times within 64ms. The time required to complete the auto refresh operation is specified by tRc(min.). To provide the AutoRefresh command, all banks need to be in the idle state and the device must not be in power down mode (CKE is high in the previous cycle). This command must be followed by NOPs until the auto refresh operation is completed. The precharge time requirement, tRP(min), must be met before successive auto refresh operations are performed.

### 13 SelfRefresh Entry command

(RAS# = "L", CAS# = "L", WE# = "H", CKE = "L", A0-A12 = Don't care)

The SelfRefresh is another refresh mode available in the SDRAM. It is the preferred refresh mode for data retention and low power operation. Once the SelfRefresh command is registered, all the inputs to the SDRAM become "don't care" with the exception of CKE, which must remain LOW. The refresh addressing and timing is internally generated to reduce power consumption. The SDRAM may remain in SelfRefresh mode for an indefinite period. The SelfRefresh mode is exited by restarting the external clock and then asserting HIGH on CKE (SelfRefresh Exit command).

#### 14 SelfRefresh Exit command

This command is used to exit from the SelfRefresh mode. Once this command is registered, NOP or Device Deselect commands must be issued for  $t_{RC}(min.)$  because time is required for the completion of any bank currently being internally refreshed. If auto refresh cycles in bursts are performed during normal operation, a burst of 4096 auto refresh cycles should be completed just prior to entering and just after exiting the SelfRefresh mode.

### 15 Clock Suspend Mode Entry / PowerDown Mode Entry command (CKE = "L")

When the SDRAM is operating the burst cycle, the internal CLK is suspended(masked) from the subsequent cycle by issuing this command (asserting CKE "LOW"). The device operation is held intact while CLK is suspended. On the other hand, when all banks are in the idle state, this command performs entry into the PowerDown mode. All input and output buffers (except the CKE buffer) are turned off in the PowerDown mode. The device may not remain in the Clock Suspend or PowerDown state longer than the refresh period (64ms) since the command does not perform any refresh operations.

### 16 Clock Suspend Mode Exit / PowerDown Mode Exit command (CKE= "H")

When the internal CLK has been suspended, the operation of the internal CLK is reinitiated from the subsequent cycle by providing this command (asserting CKE "HIGH"). When the device is in the PowerDown mode, the device exits this mode and all disabled buffers are turned on to the active state. tpde(min.) is required when the device exits from the PowerDown mode. Any subsequent commands can be issued after one clock cycle from the end of this command.

#### 17 Data Write / Output Enable, Data Mask / Output Disable command (DQM = "L", "H")

During a write cycle, the DQM signal functions as a Data Mask and can control every word of the input data. During a read cycle, the DQM functions as the controller of output buffers. DQM is also used for device selection, byte selection and bus control in a memory system.

# **Absolute Maximum Rating**

| Symbol    | Item                              | Rating                   | Unit | Note |

|-----------|-----------------------------------|--------------------------|------|------|

| VIN, VOUT | Input, Output Voltage             | - 0.5 ~ 4.6 V            |      | 1    |

| Vdd, Vddq | Power Supply Voltage              | ply Voltage -0.5 ~ 4.6 V |      | 1    |

| TA        | Operating Temperature             | 0 ~ 70                   | °C   | 1    |

| Tstg      | Storage Temperature               | - 65 ~ 150               | °C   | 1    |

| Tsolder   | Soldering Temperature (10 second) | 260                      | °C   | 1    |

| PD        | Power Dissipation                 | 1                        | W    | 1    |

| Іоит      | Short Circuit Output Current      | 50                       | mA   | 1    |

# Recommended D.C. Operating Conditions ( $T_A = 0 \sim 70^{\circ}$ C)

| Symbol    | Parameter                            | Min.  | Тур. | Max.                  | Unit | Note |

|-----------|--------------------------------------|-------|------|-----------------------|------|------|

| $V_{DD}$  | Power Supply Voltage                 | 3.0   | 3.3  | 3.6                   | V    | 2    |

| $V_{DDQ}$ | Power Supply Voltage(for I/O Buffer) | 3.0   | 3.3  | 3.6                   | V    | 2    |

| VIH       | LVTTL Input High Voltage             | 2.0   | 3.0  | V <sub>DDQ</sub> +0.3 | V    | 2    |

| VIL       | LVTTL Input Low Voltage              | - 0.3 | 0    | 0.8                   | V    | 2    |

## Capacitance (V<sub>DD</sub> = 3.3V, f = 1MHz, Ta = 25°C)

| Symbol           | Parameter                | Min. | Max. | Unit |

|------------------|--------------------------|------|------|------|

| Сі               | Input Capacitance        | 2.5  | 5    | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance | 4    | 6.5  | pF   |

Note: These parameters are periodically sampled and are not 100% tested.

# Recommended D.C. Operating Conditions (V<sub>DD</sub> = $3.3V \pm 0.3V$ , T<sub>A</sub> = $0 \sim 70^{\circ}$ C)

|                                                                                                | - 6/7             |         |      |      |

|------------------------------------------------------------------------------------------------|-------------------|---------|------|------|

| Description/Test condition                                                                     | Symbol            | Max.    | Unit | Note |

| Operating Current                                                                              |                   |         |      | _    |

| tRc ≥ tRc(min), Outputs Open                                                                   | IDD1              | 130/130 |      | 3    |

| One bank active                                                                                | 1001              |         |      |      |

| Precharge Standby Current in non-power down mode                                               |                   |         |      |      |

| $tck = tck(min), CS\# \ge V_{IH}(min), CKE \ge V_{IH}$                                         | I <sub>DD2N</sub> | 20      |      | 3    |

| Input signals are changed very 2clks                                                           |                   |         |      |      |

| Precharge Standby Current in non-power down mode                                               | _                 | 15      |      |      |

| Tck = $\infty$ , CLK $\leq$ V <sub>IL</sub> (max), CKE $\geq$ V <sub>IH</sub>                  | IDD2NS            | 15      |      |      |

| Precharge Standby Current in power down mode                                                   |                   | 2       |      | 3    |

| $t_{CK} = tck(min), CKE \le V_{IL}(max)$                                                       | IDD2P             | ۷       |      | 3    |

| Precharge Standby Current in power down mode                                                   |                   | 1       |      |      |

| T <sub>CK</sub> = ∞, CKE ≤ V <sub>IL</sub> (max)                                               | IDD2PS            | ı       | mΑ   |      |

| Active Standby Current in non-power down mode                                                  |                   |         |      |      |

| tck = tck(min), CKE $\geq$ VIH(min), CS# $\geq$ VIH(min)                                       | IDD3N             | 30      |      |      |

| Input signals are changed very 2clks                                                           |                   |         |      |      |

| Active Standby Current in non-power down mode                                                  |                   | 20      |      |      |

| CKE $\geq$ V <sub>IH</sub> (min), CLK $\leq$ V <sub>IL</sub> (max), t <sub>CK</sub> = $\infty$ | IDD3NS            | 20      |      |      |

| Operating Current (Burst mode)                                                                 | _                 | 160/160 |      | 3, 4 |

| tcк =tcк(min), Outputs Open, Multi-bank interleave                                             | IDD4              | 160/160 |      | 3, 4 |

| Refresh Current                                                                                |                   | 160     |      | 3    |

| $t_{RC} \ge t_{RC}(min)$                                                                       | I <sub>DD5</sub>  | 100     |      |      |

| Self Refresh Current                                                                           |                   | 3       |      |      |

| $V_{IH} \geq V_{DD} \text{ - } 0.2,  0V \leq V_{IL} \leq 0.2V$                                 | I <sub>DD6</sub>  | 3       |      |      |

| Parameter | Description                                                                                 | Min. | Max. | Unit | Note |

|-----------|---------------------------------------------------------------------------------------------|------|------|------|------|

| lıL       | Input Leakage Current ( $0V \le V_{IN} \le V_{DD}$ , All other pins not under test = $0V$ ) | - 10 | 10   | μА   |      |

| lol       | Output Leakage Current Output disable, $0V \le V_{DDQ}$ )                                   | - 10 | 10   | μΑ   |      |

| Vон       | LVTTL Output "H" Level Voltage 2.4 - ( Iout = -2mA )                                        |      | -    | V    |      |

| Vol       | LVTTL Output "L" Level Voltage<br>(lou⊤ = 2mA)                                              | -    | 0.4  | V    |      |

### **Electrical Characteristics and Recommended A.C. Operating Conditions**

$(V_{DD} = 3.3V \pm 0.3V, T_A = 0 \sim 70^{\circ}C)$  (Note: 5, 6, 7, 8)

|                  | nbol A.C. Parameter                                  |         | -6/7    |        |      |      |

|------------------|------------------------------------------------------|---------|---------|--------|------|------|

| Symbol           |                                                      |         | Min.    | Max.   | Unit | Note |

| trc              | Row cycle time (same bank)                           |         | 60/63   |        |      |      |

| <b>t</b> RFC     | Refresh cycle time                                   |         | 60/70   |        |      |      |

| trcd             | RAS# to CAS# delay (same bank)                       |         | 15/20   |        |      |      |

| <b>t</b> RP      | Precharge to refresh/row activate of (same bank)     | command | 15/20   |        |      |      |

| t <sub>RRD</sub> | Row activate to row activate delay (different banks) |         | 12/14   |        |      |      |

| <b>t</b> RSC     | Mode register set cycle time                         |         | 12/14   |        |      |      |

| tras             | Row activate to precharge time (same bank)           |         | 42/45   | 120000 |      |      |

| twR              | Write recovery time                                  |         | 12/14   |        |      |      |

| tck2             | Clask avalations                                     | CL* = 2 | -/12    |        | ns   | 9    |

| <b>t</b> ck3     | Clock cycle time                                     | CL* = 3 | 6/7     |        |      |      |

| tсн              | Clock high time                                      |         | 2/2.5   |        |      | 10   |

| <b>t</b> CL      | Clock low time                                       |         | 2/2.5   |        |      | 10   |

| t <sub>AC2</sub> | Access time from CLK                                 | CL* = 2 |         | -/6.5  |      | 10   |

| tаcз             | (positive edge)                                      | CL* = 3 |         | 5/5.4  |      | 10   |

| tон              | Data output hold time                                |         | 2.5/2.7 |        |      | 9    |

| tız              | Data output low impedance                            |         | 0       |        |      |      |

| tHZ              | Data output high impedance                           |         | 2.5/2.7 | 5/5.4  |      | 8    |

| tıs              | Data/Address/Control Input set-up time               |         | 1.8/1.8 |        |      | 10   |

| tıн              | Data/Address/Control Input hold time                 |         | 1       |        |      | 10   |

| t⊤               | Transition time of CLK                               |         | 1       | 10     |      |      |

| tref             | Refresh interval time                                |         |         | 7.8    | μs   |      |

<sup>\*</sup> CL is CAS# Latency.

### Note:

- 1. Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

- 2. All voltages are referenced to Vss. Overshoot VIH(Max) = VDD+2.0V for pulse width  $\leq$  3ns. Undershoot VIL(Min) = -2.0V for pulse width  $\leq$  3ns.

- 3. These parameters depend on the cycle rate and these values are measured by the cycle rate under the minimum value of tck and tcc. Input signals are changed one time during tck.

19

- 4. These parameters depend on the output loading. Specified values are obtained with the output open.

- 5. Power-up sequence is described in Note 11.

#### 6. A.C. Test Conditions

### **LVTTL Interface**

| Reference Level of Output Signals                | 1.4V / 1.4V |

|--------------------------------------------------|-------------|

| Input Signal Levels                              | 2.4V / 0.4V |

| Transition Time (Rise and Fall) of Input Signals | 1ns         |

| Reference Level of Input Signals                 | 1.4V        |

### **Output Loading**

- 7. Transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>. Transition(rise and fall) of input signals are in a fixed slope (1 ns).

- 8. thz defines the time in which the outputs achieve the open circuit condition and are not at reference levels.

- 9. If clock rising time is longer than 1 ns, ( $t_R/2-0.5$ ) ns should be added to the parameter.

- 10. Assumed input rise and fall time  $t_T$  (  $t_R \& t_F$  ) = 1 ns

If  $t_R$  or  $t_F$  is longer than 1 ns, transient time compensation should be considered, i.e., [(tr + tf)/2 - 1] ns should be added to the parameter.

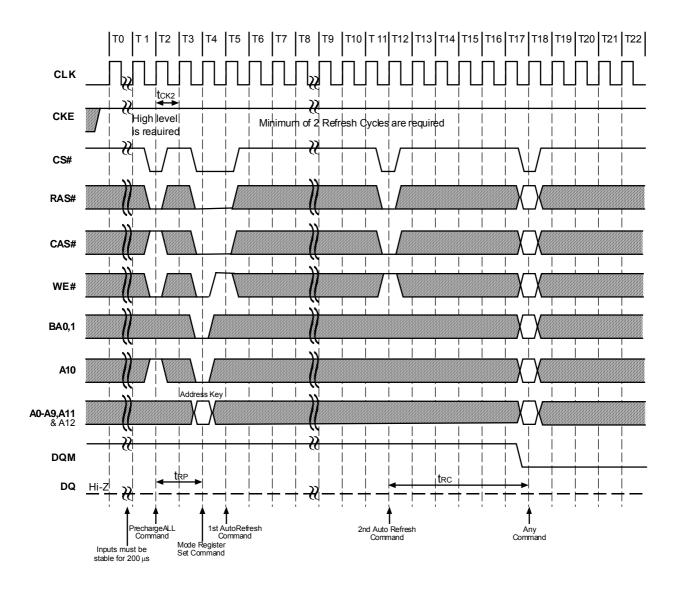

### 11. Power up Sequence

Power up must be performed in the following sequence.

- 1) Power must be applied to VDD and VDDQ(simultaneously) when all input signals are held "NOP" state and both CKE = "H" and DQM = "H." The CLK signals must be started at the same time.

- 2) After power-up, a pause of 200μseconds minimum is required. Then, it is recommended that DQM is held "HIGH" (VDD levels) to ensure DQ output is in high impedance.

- 3) All banks must be precharged.

- 4) Mode Register Set command must be asserted to initialize the Mode register.

- 5) A minimum of 2 Auto-Refresh dummy cycles must be required to stabilize the internal circuitry of the device.

### **Timing Waveforms**

Figure 1. AC Parameters for Write Timing (Burst Length=4, CAS# Latency=2)

Figure 2. AC Parameters for Read Timing (Burst Length=2, CAS# Latency=2)

22

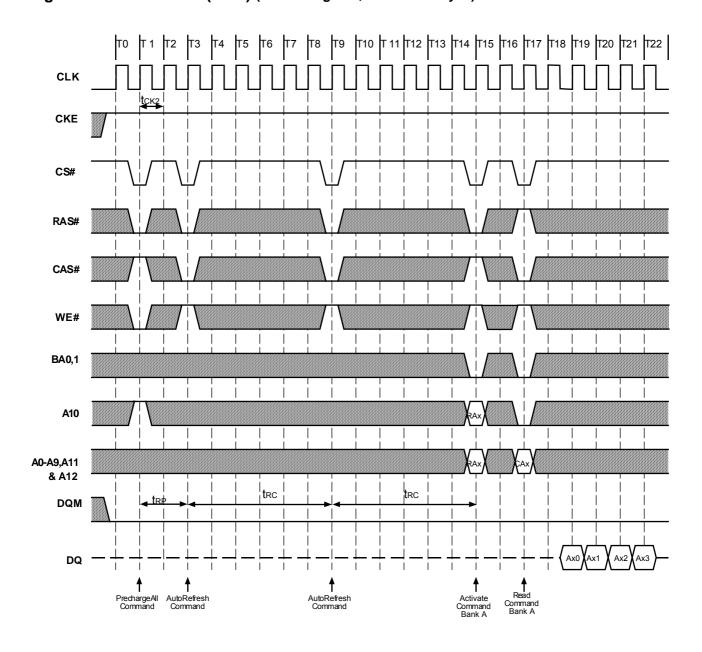

Figure 3. Auto Refresh (CBR) (Burst Length=4, CAS# Latency=2)

Figure 4. Power on Sequence and Auto Refresh (CBR)

T9 T10 T11 T12 T15 \*Note 3 **CKE** tsax \*Note 5 CS# RAS# \*Note 8 CAS# **BA0,1** A0-A9,A11 & A12 WE# DQM DQ

Figure 5. Self Refresh Entry & Exit Cycle

### Note: To Enter SelfRefresh Mode

Self Refresh Enter

- 1. CS#, RAS# & CAS# with CKE should be low at the same clock cycle.

- 2. After 1 clock cycle, all the inputs including the system clock can be don't care except for CKE.

- 3. The device remains in SelfRefresh mode as long as CKE stays "low".

Once the device enters SelfRefresh mode, minimum t<sub>RAS</sub> is required before exit from SelfRefresh.

### To Exit SelfRefresh Mode

- 1. System clock restart and be stable before returning CKE high.

- 2. Enable CKE and CKE should be set high for minimum time of tsrx.

- 3. CS# starts from high.

- 4. Minimum tRC is required after CKE going high to complete SelfRefresh exit.

- 5. 2048 cycles of burst AutoRefresh is required before SelfRefresh entry and after SelfRefresh exit if the system uses burst refresh.

SelfRefresh Exit

AutoRefresh

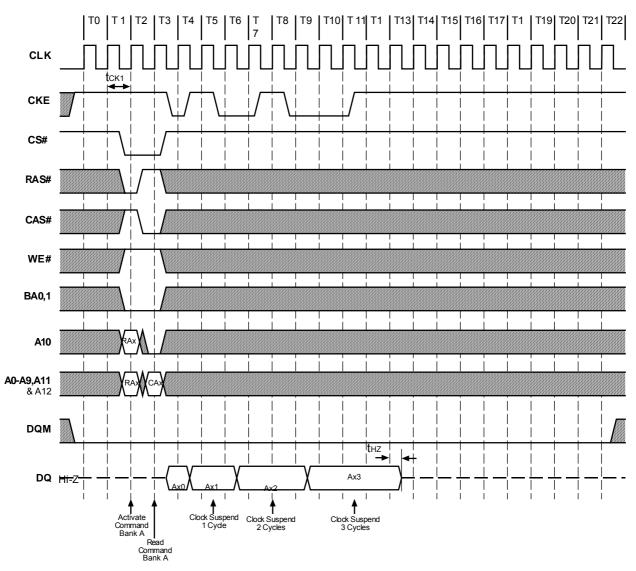

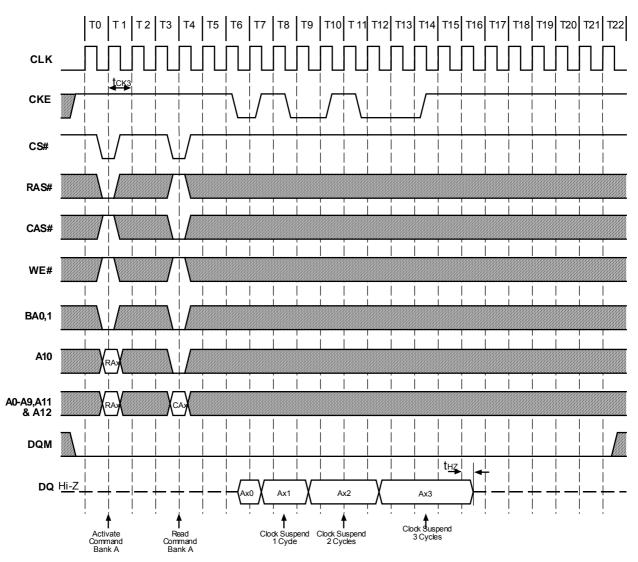

Figure 6.1. Clock Suspension During Burst Read (Using CKE) (Burst Length=4, CAS# Latency=1)

Figure 6.2. Clock Suspension During Burst Read (Using CKE) (Burst Length=4, CAS# Latency=2)

Figure 6.3. Clock Suspension During Burst Read (Using CKE) (Burst Length=4, CAS# Latency=3)

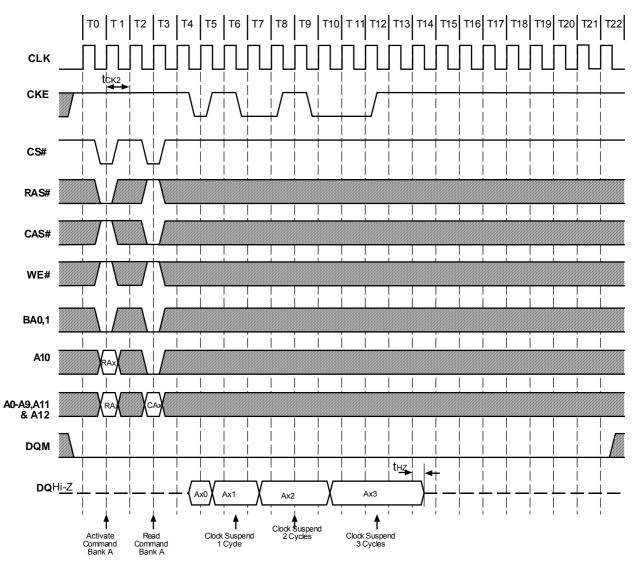

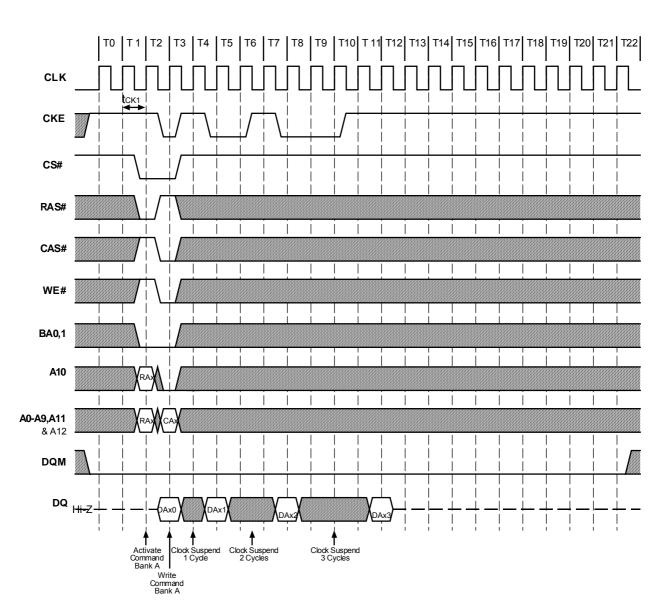

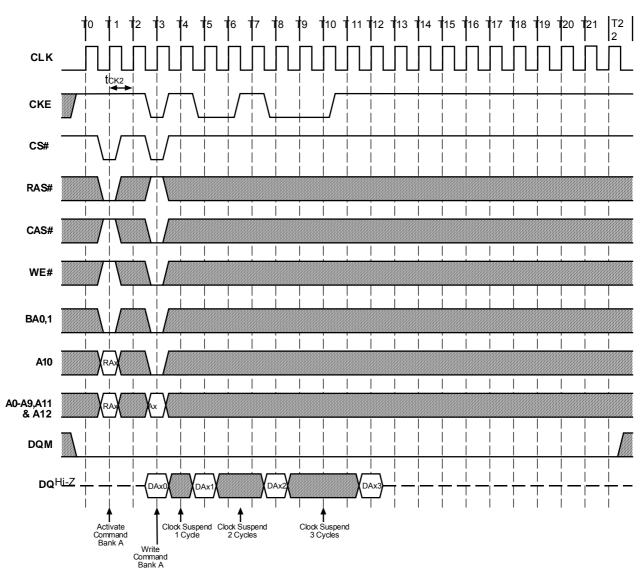

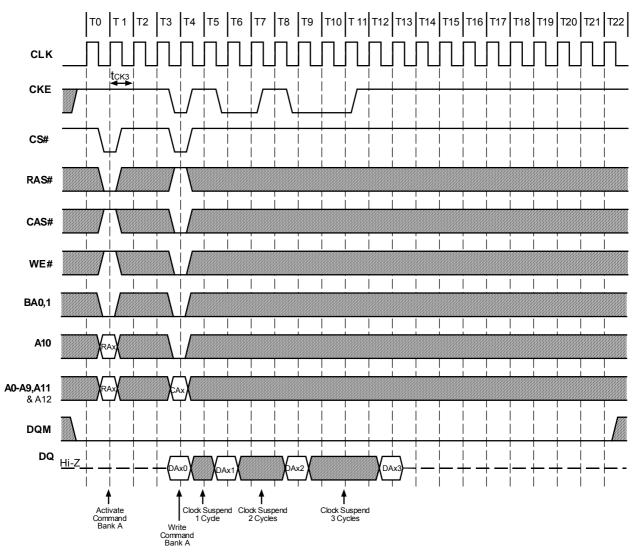

Figure 7.1. Clock Suspension During Burst Write (Using CKE)

(Burst Length = 4, CAS# Latency = 1)

Figure 7.2. Clock Suspension During Burst Write (Using CKE) (Burst Length=4, CAS# Latency=2)

Figure 7.3. Clock Suspension During Burst Write (Using CKE) (Burst Length=4, CAS# Latency=3)

T10 T 11 T12 T13 T14 T15 T16 T17 T18 T19 T20 T21 T22 CLK tck2 CKE Valid CS# RAS# CAS# WE# BA0,1 A10 A0~A9,A11 & A12 DQM tHZ Ax1 DQ ACTIVE STANDBY PRECHARGE STANDBY Read Command Bank A Activate Command Bank A Clock Mask Start Clock Mask End Precharge Command Bank A Power Down Mode Entry Any Command Power Down Mode Exit

Figure 8. Power Down Mode and Clock Mask (Burst Length=4, CAS# Latency=2)

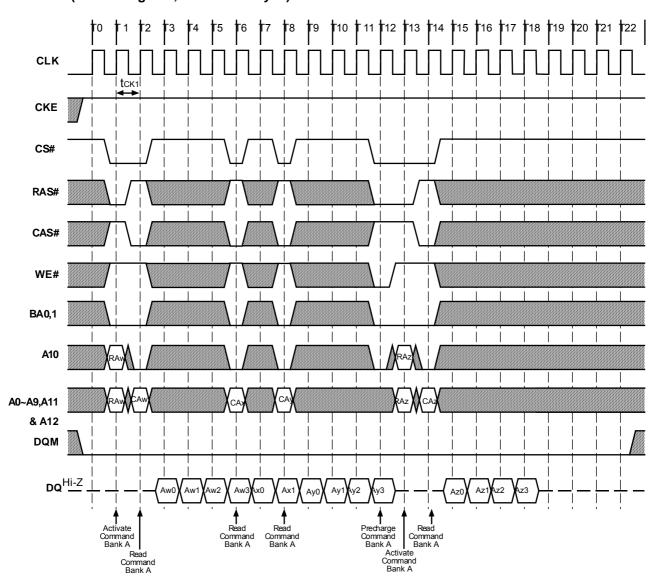

Figure 9.1. Random Column Read (Page within same Bank) (Burst Length=4, CAS# Latency=1)

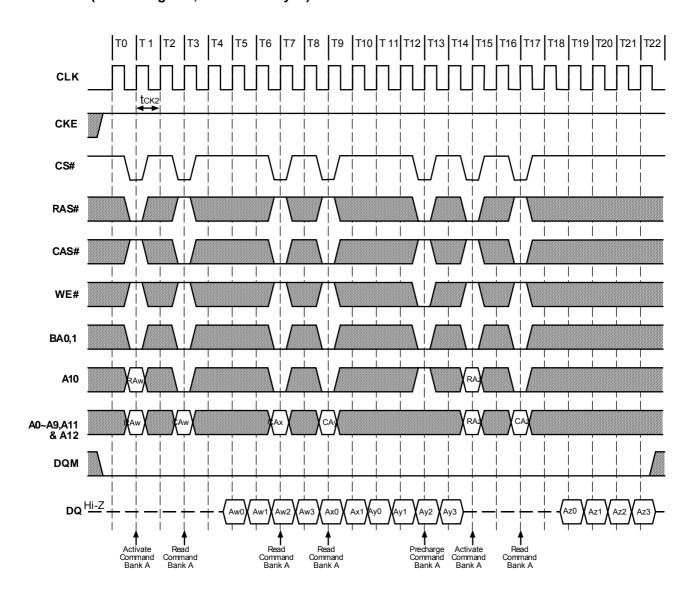

Figure 9.2. Random Column Read (Page within same Bank) (Burst Length=4, CAS# Latency=2)

Figure 9.3. Random Column Read (Page within same Bank) (Burst Length=4, CAS# Latency=3)

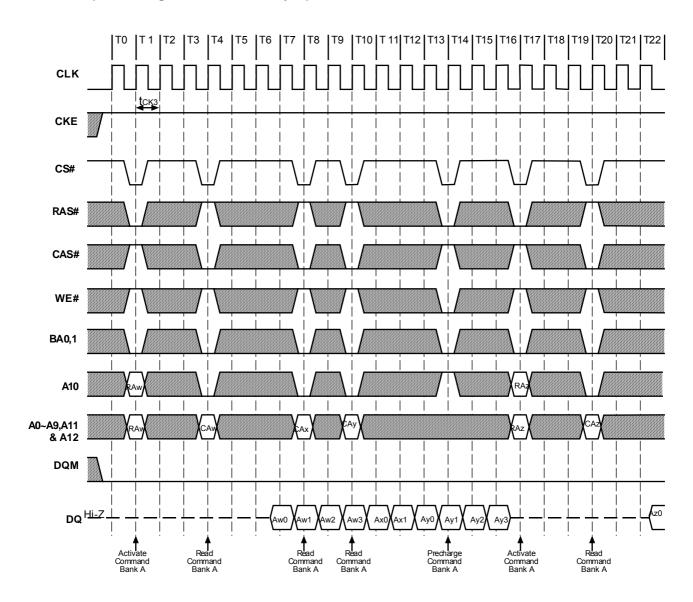

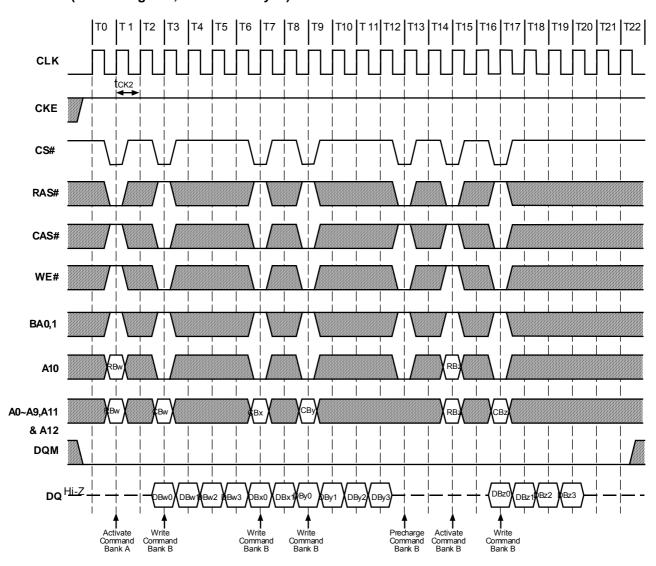

Figure 10.1. Random Column Write (Page within same Bank) (Burst Length=4, CAS# Latency=1)

Figure 10.2. Random Column Write (Page within same Bank) (Burst Length=4, CAS# Latency=2)

Figure 10.3. Random Column Write (Page within same Bank) (Burst Length=4, CAS# Latency=3)

38

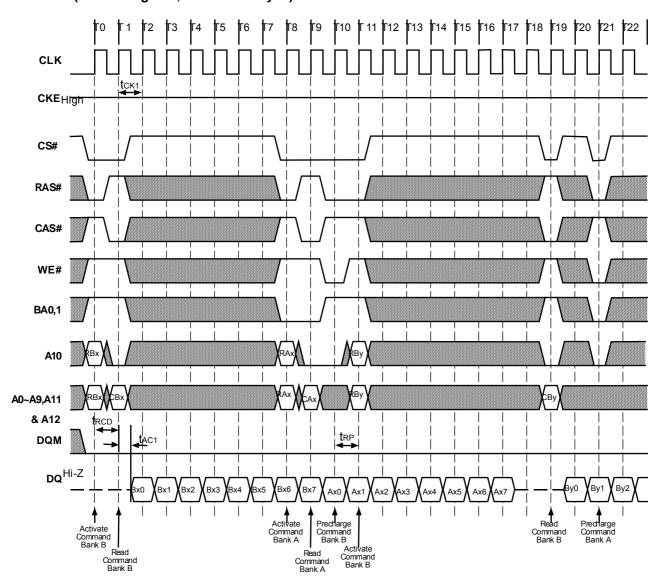

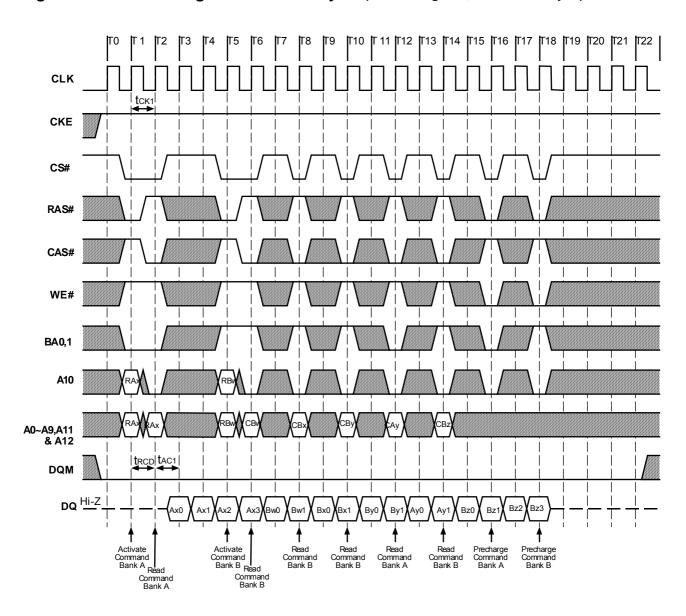

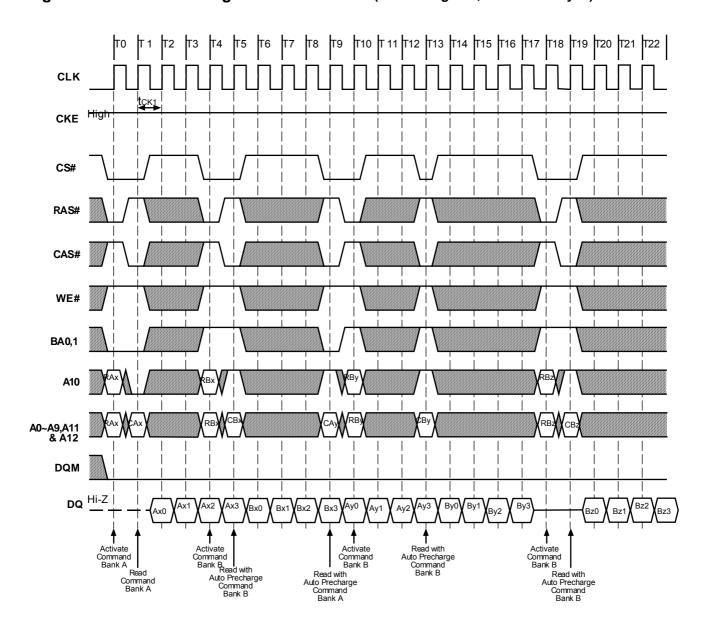

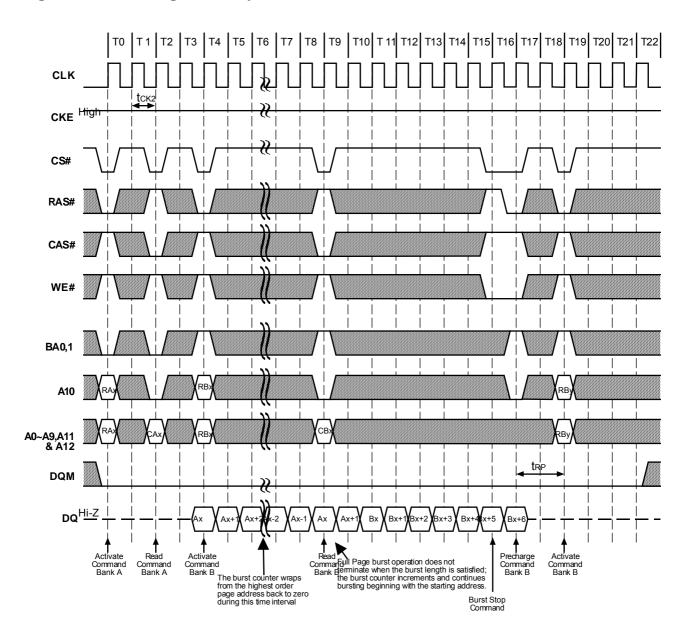

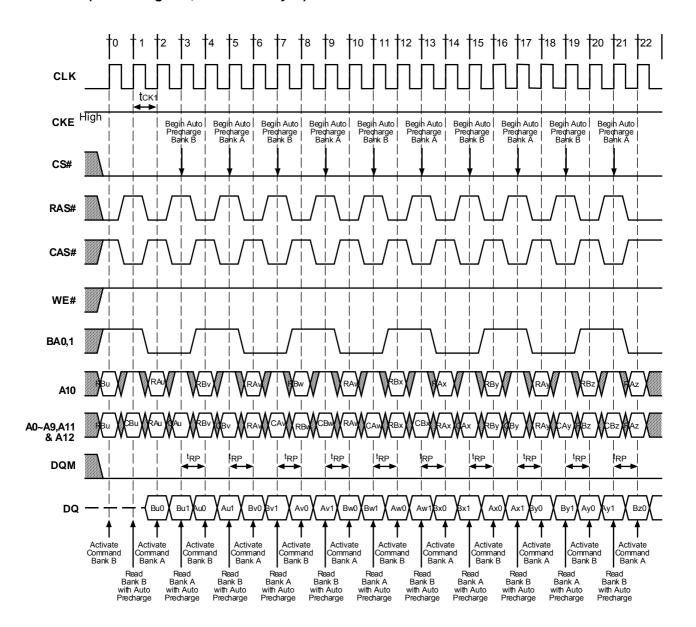

Figure 11.1. Random Row Read (Interleaving Banks) (Burst Length=8, CAS# Latency=1)

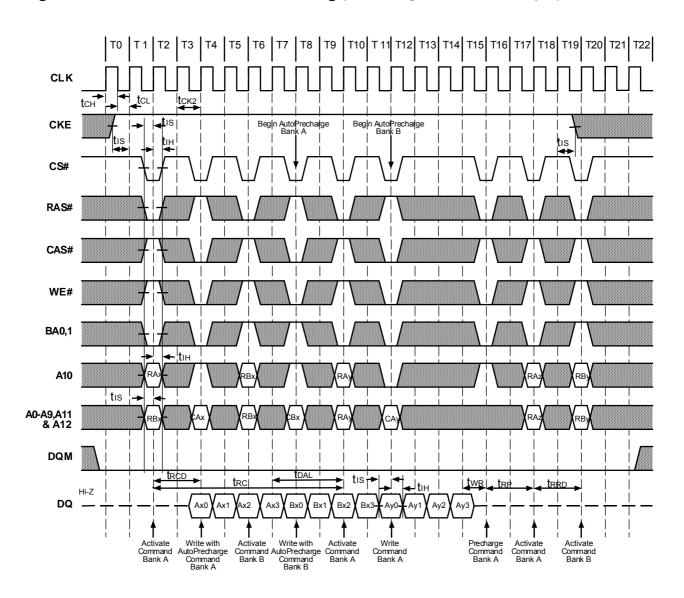

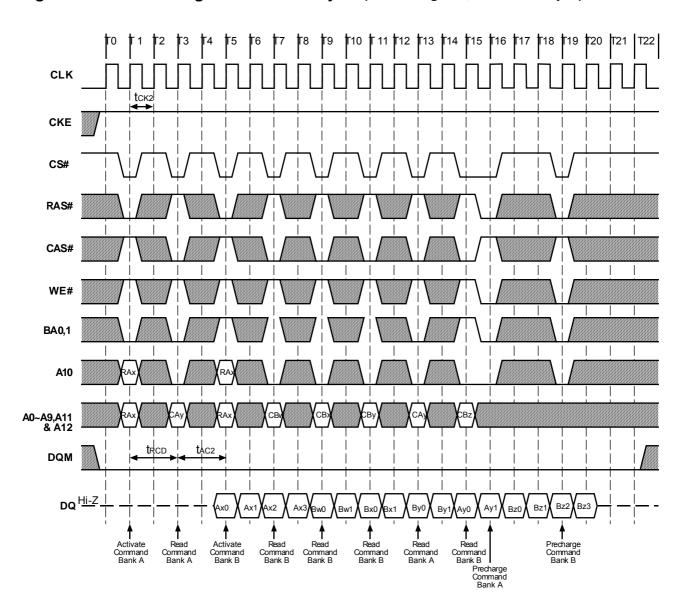

Figure 11.2. Random Row Read (Interleaving Banks) (Burst Length=8, CAS# Latency=2)

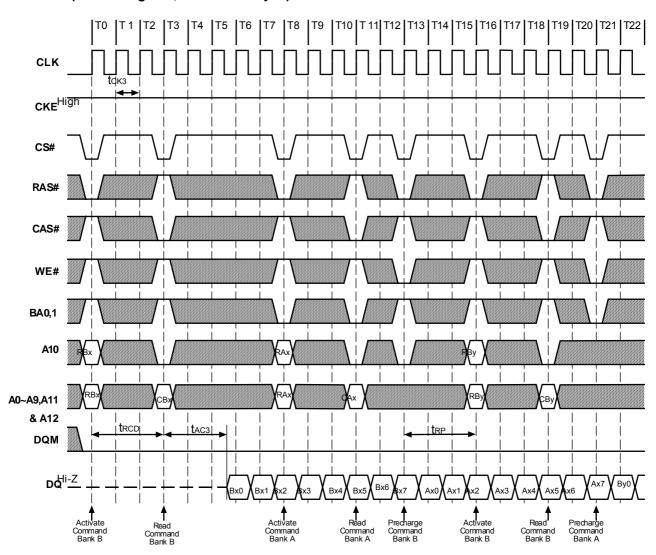

Figure 11.3. Random Row Read (Interleaving Banks)

(Burst Length=8, CAS# Latency=3)

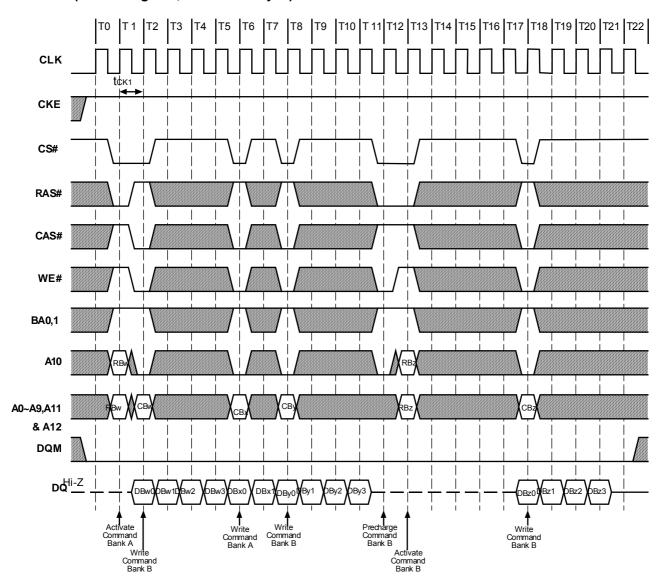

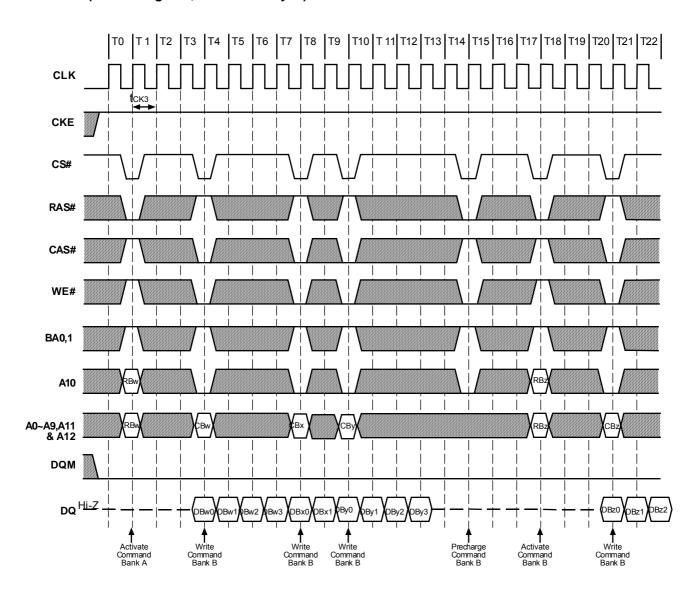

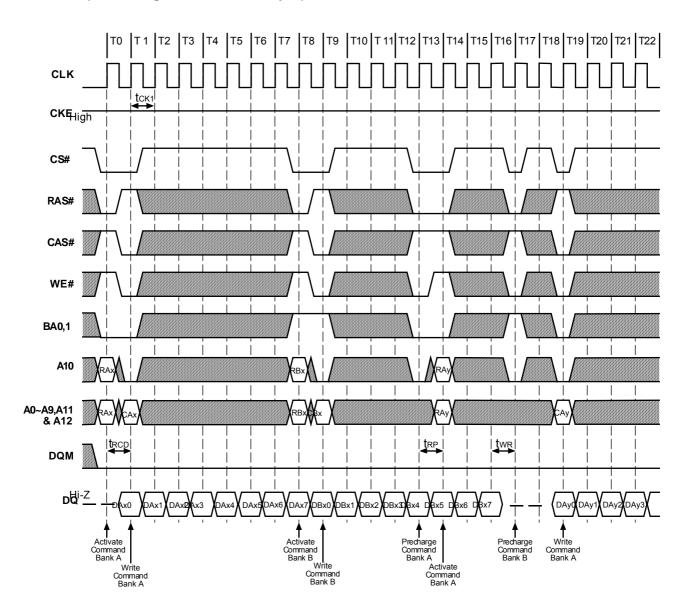

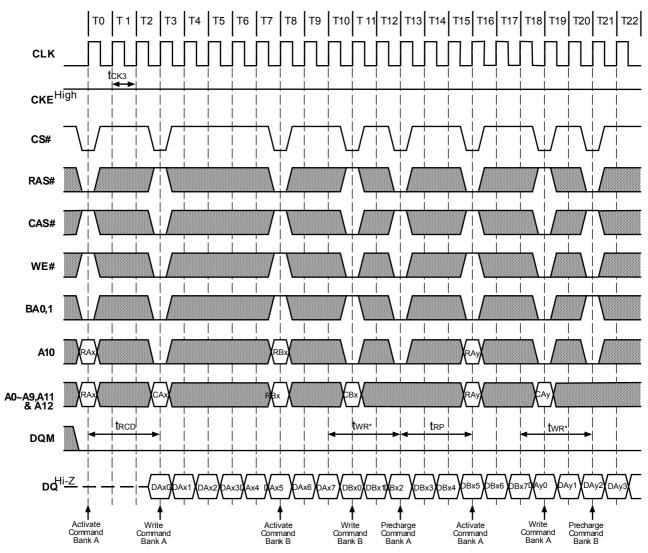

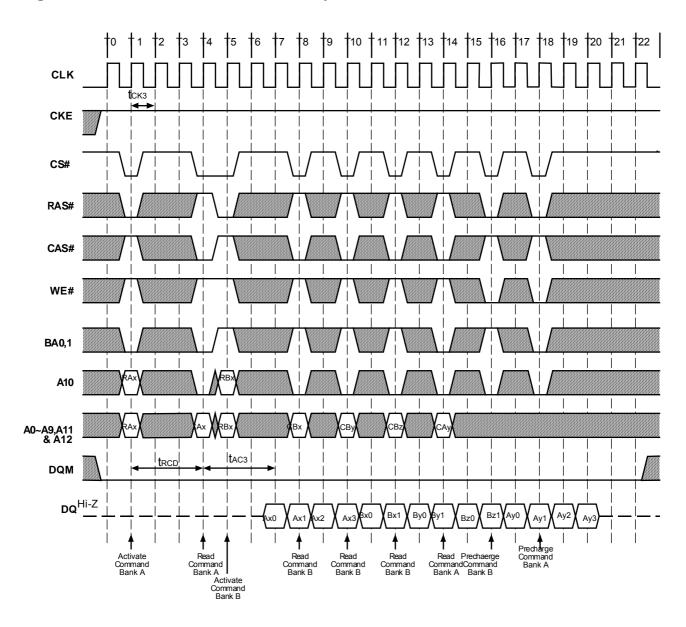

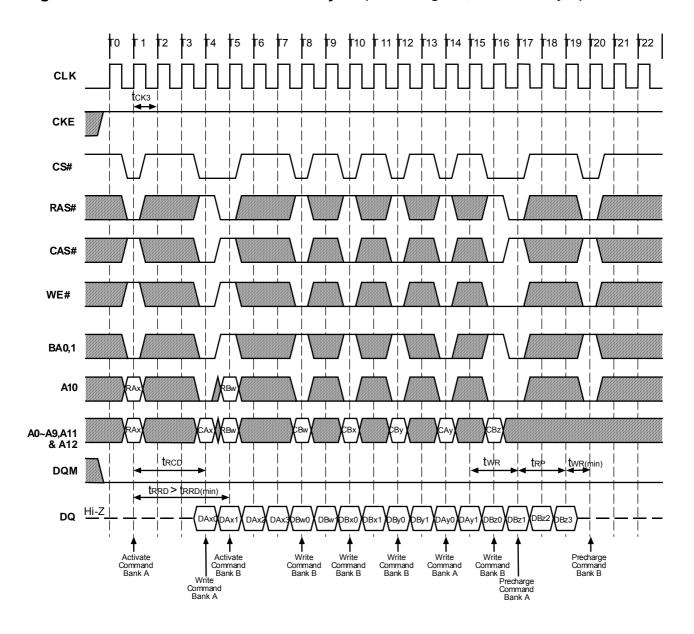

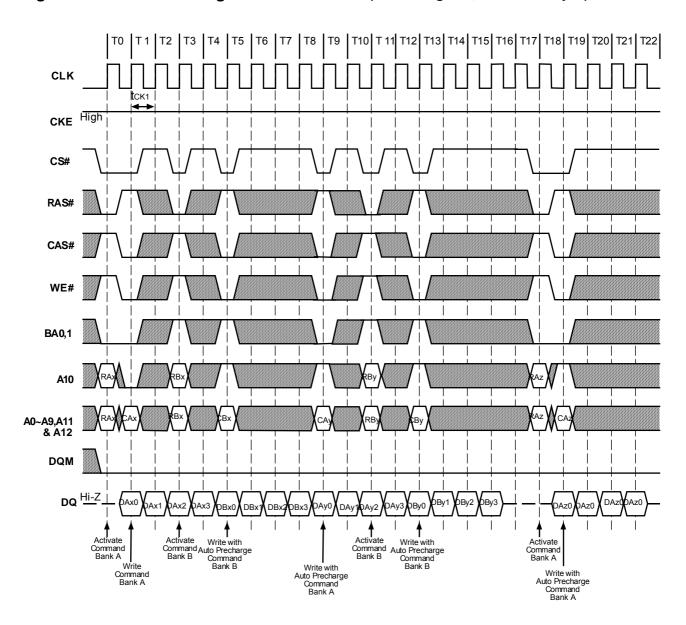

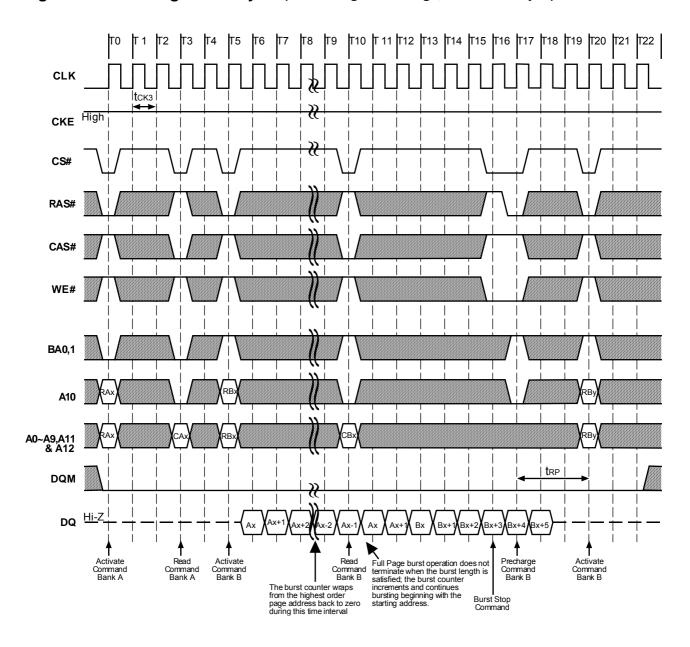

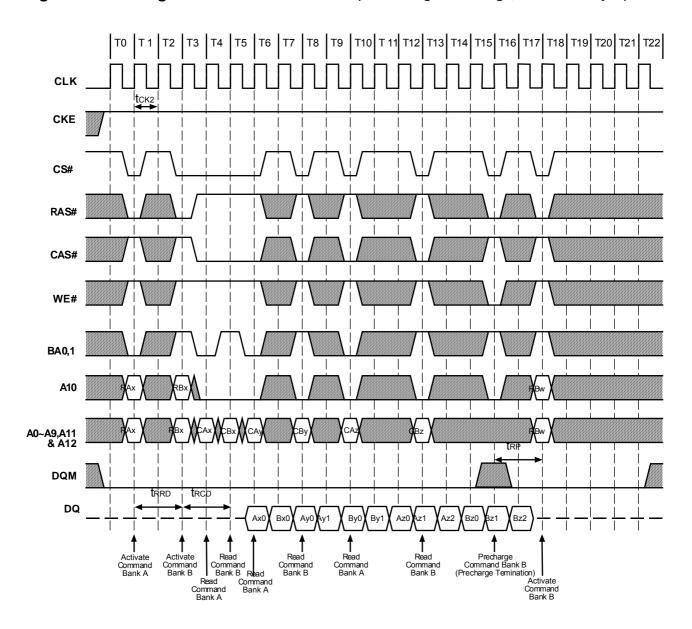

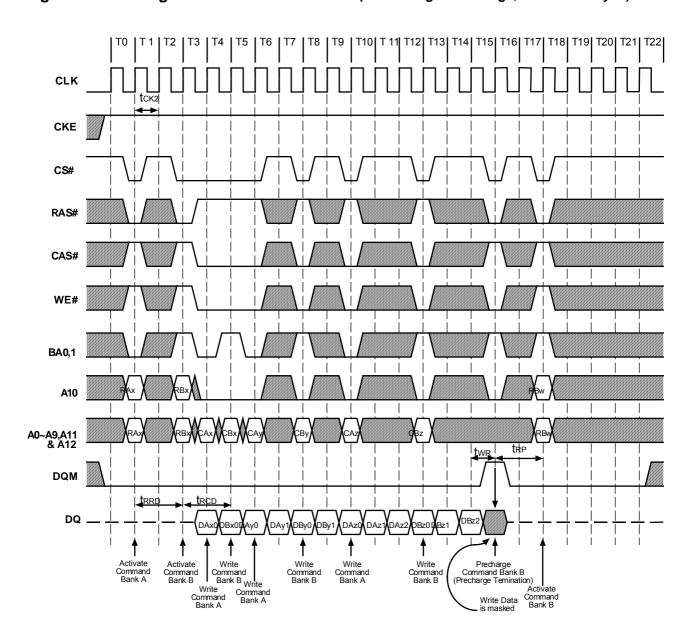

Figure 12.1. Random Row Write (Interleaving Banks)

(Burst Length=8, CAS# Latency=1)

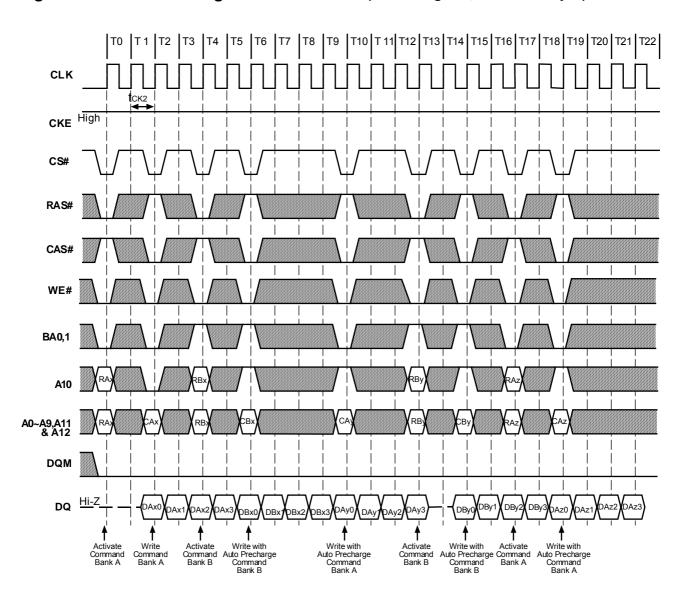

Figure 12.2. Random Row Write (Interleaving Banks) (Burst Length=8, CAS# Latency=2)

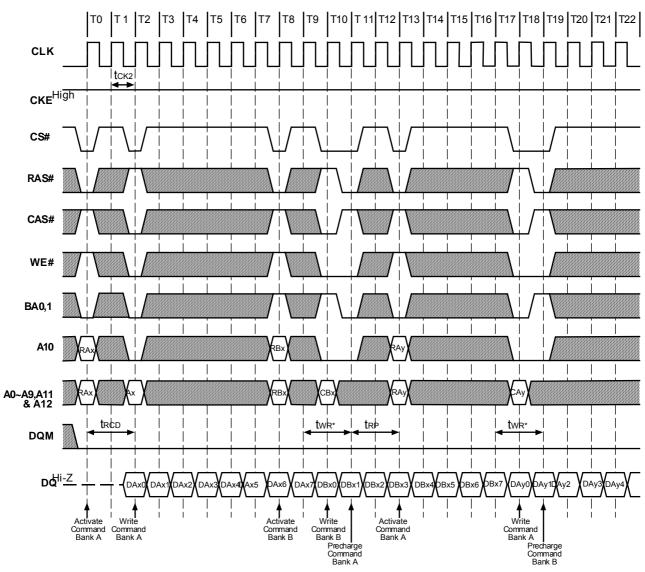

<sup>\*</sup> twr > twr(min.)

Figure 12.3. Random Row Write (Interleaving Banks) (Burst Length=8, CAS# Latency=3)

<sup>\*</sup> twr > twr(min.)

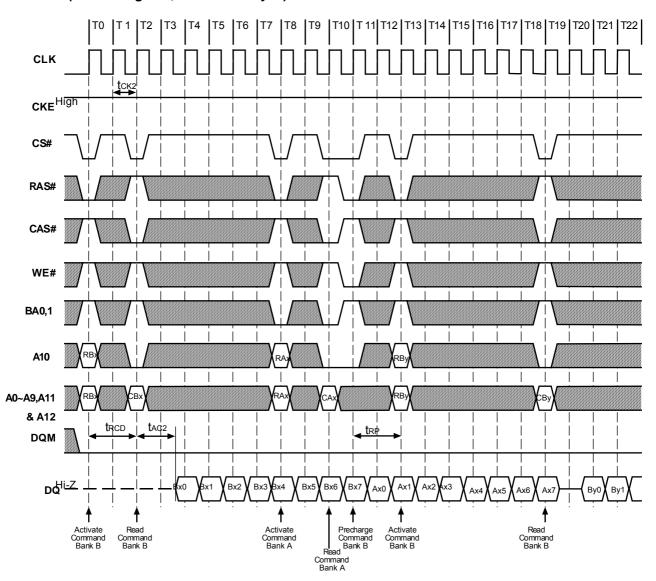

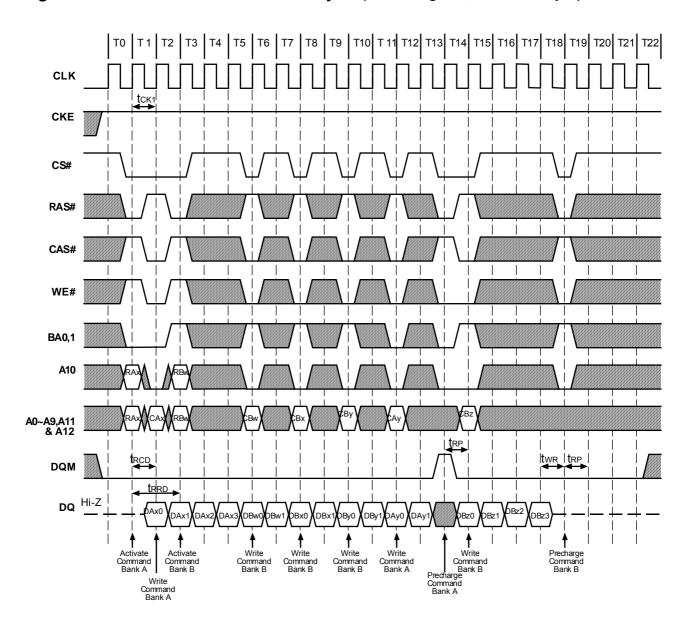

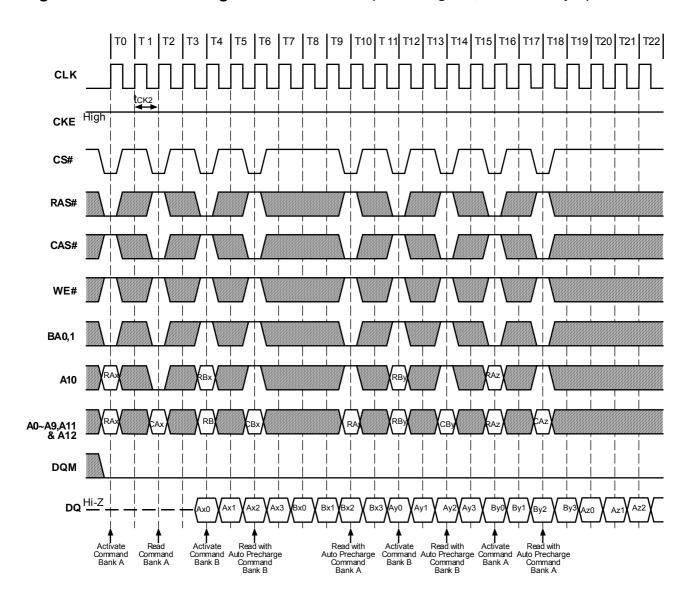

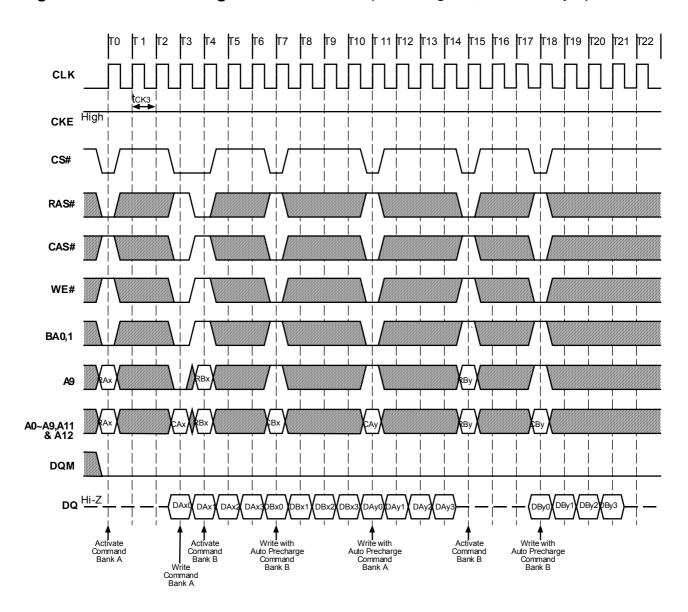

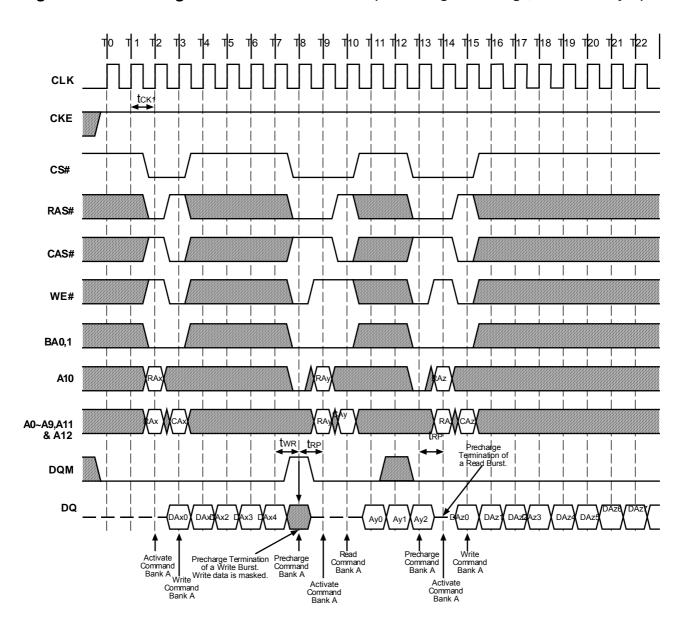

Figure 13.1. Read and Write Cycle (Burst Length=4, CAS# Latency=1)

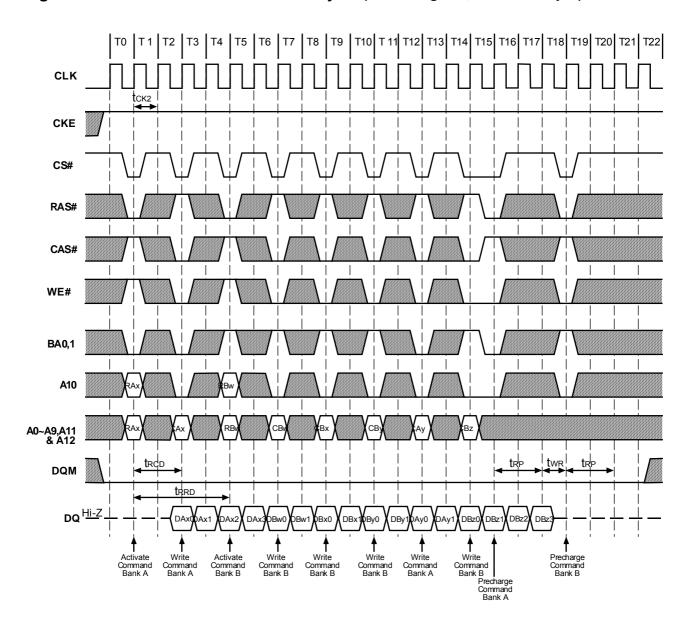

Figure 13.2. Read and Write Cycle (Burst Length=4, CAS# Latency=2)

Figure 13.3. Read and Write Cycle (Burst Length=4, CAS# Latency=3)

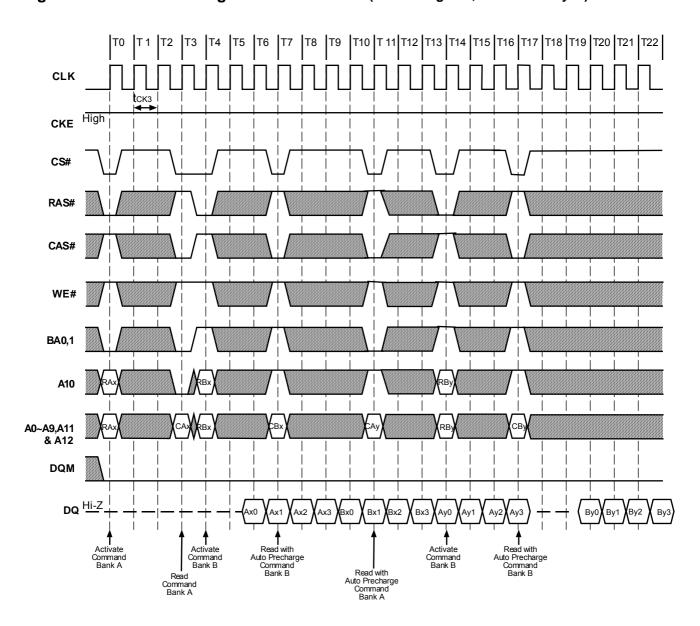

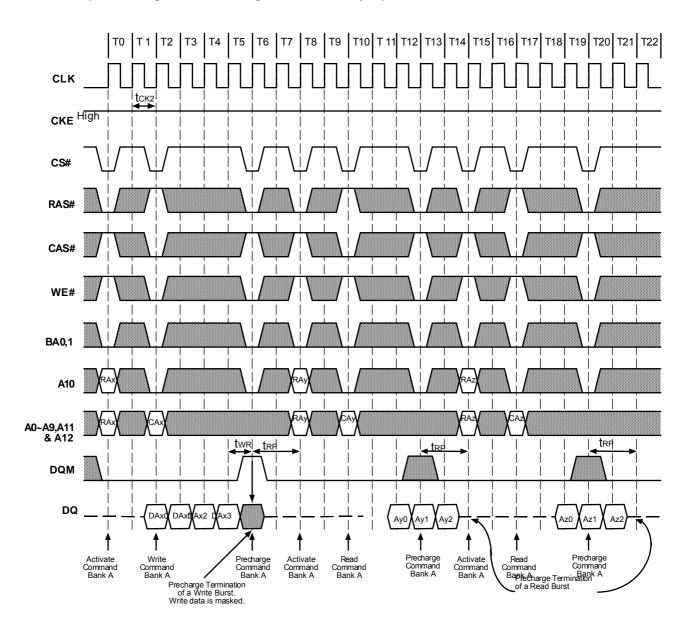

Figure 14.1. Interleaving Column Read Cycle (Burst Length=4, CAS# Latency=1)

Figure 14.2. Interleaving Column Read Cycle (Burst Length=4, CAS# Latency=2)

Figure 14.3. Interleaved Column Read Cycle (Burst Length=4, CAS# Latency=3)

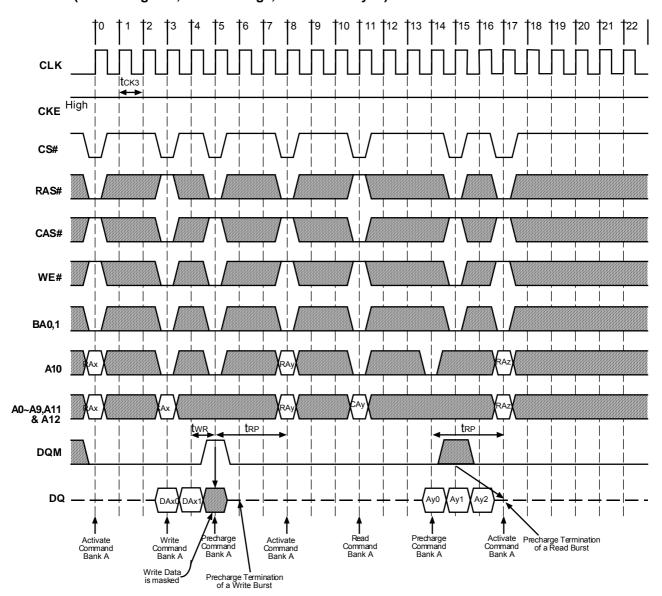

50

Figure 15.1. Interleaved Column Write Cycle (Burst Length=4, CAS# Latency=1)

Figure 15.2. Interleaved Column Write Cycle (Burst Length=4, CAS# Latency=2)

Figure 15.3. Interleaved Column Write Cycle (Burst Length=4, CAS# Latency=3)

Figure 16.1. Auto Precharge after Read Burst (Burst Length=4, CAS# Latency=1)

Figure 16.2. Auto Precharge after Read Burst (Burst Length=4, CAS# Latency=2)

Figure 16.3. Auto Precharge after Read Burst (Burst Length=4, CAS# Latency=3)

Figure 17.1. Auto Precharge after Write Burst (Burst Length=4, CAS# Latency=1)

Figure 17.2. Auto Precharge after Write Burst (Burst Length=4, CAS# Latency=2)

Figure 17.3. Auto Precharge after Write Burst (Burst Length=4, CAS# Latency=3)

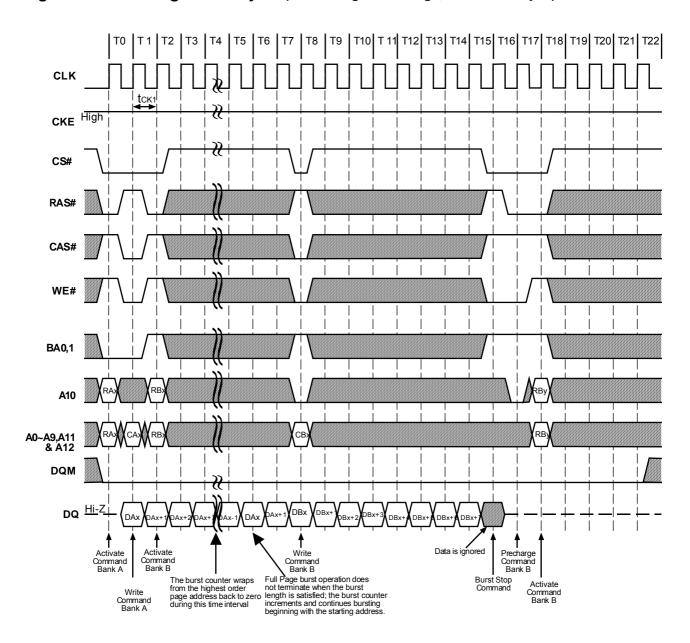

Figure 18.1. Full Page Read Cycle (Burst Length=Full Page, CAS# Latency=1)

Figure 18.2. Full Page Read Cycle (Burst Length=Full Page, CAS# Latency=2)

Figure 18.3. Full Page Read Cycle (Burst Length=Full Page, CAS# Latency=3)

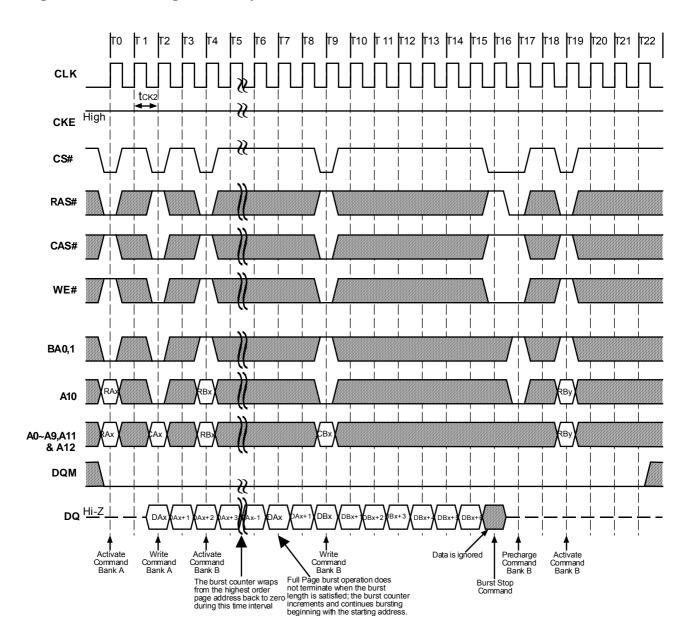

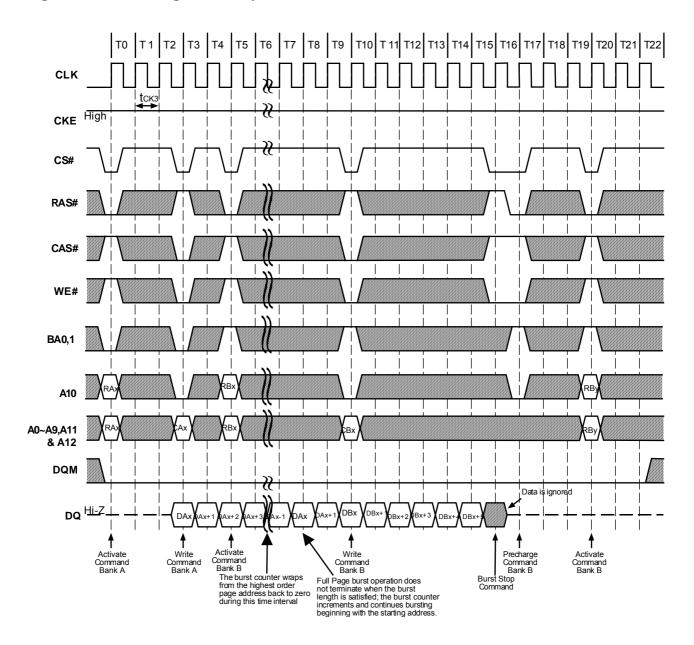

Figure 19.1. Full Page Write Cycle (Burst Length=Full Page, CAS# Latency=1)

Figure 19.2. Full Page Write Cycle (Burst Length=Full Page, CAS# Latency=2)

Figure 19.3. Full Page Write Cycle (Burst Length=Full Page, CAS# Latency=3)

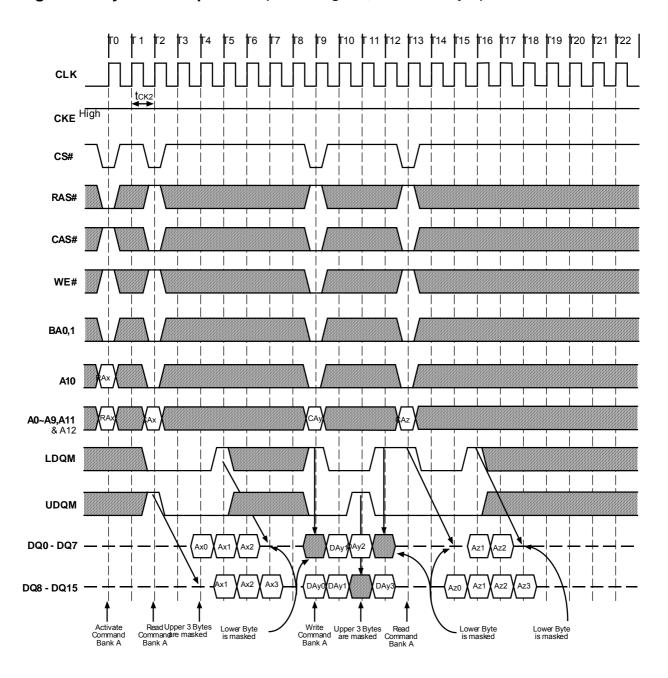

Figure 20. Byte Write Operation (Burst Length=4, CAS# Latency=2)

Figure 21. Random Row Read (Interleaving Banks)

(Burst Length=2, CAS# Latency=1)

Figure 22. Full Page Random Column Read (Burst Length=Full Page, CAS# Latency=2)

68

Figure 23. Full Page Random Column Write (Burst Length=Full Page, CAS# Latency=2)

Figure 24.1. Precharge Termination of a Burst (Burst Length=Full Page, CAS# Latency=1)

Figure 24.2. Precharge Termination of a Burst (Burst Length=8 or Full Page, CAS# Latency=2)

Figure 24.3. Precharge Termination of a Burst (Burst Length=4, 8 or Full Page, CAS# Latency=3)

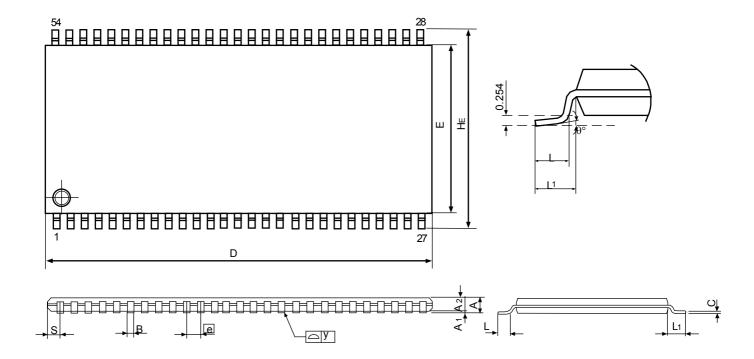

## 54 Pin TSOP II Package Outline Drawing Information

| Symbol | Dimension in inch |         |        | Dimension in mm |         |        |

|--------|-------------------|---------|--------|-----------------|---------|--------|

|        | Min               | Normal  | Max    | Min             | Normal  | Max    |

| Α      | -                 | -       | 0.047  | -               | -       | 1.194  |

| A1     | 0.002             | 0.00395 | 0.0059 | 0.05            | 0.1     | 0.150  |

| A2     | -                 | -       | 0.0411 | -               | -       | 1.044  |

| В      | 0.012             | 0.015   | 0.016  | 0.3             | 0.35    | 0.40   |

| С      | 0.0047            | 0.0065  | 0.0083 | 0.120           | 0.165   | 0.210  |

| D      | 0.872             | 0.8755  | 0.879  | 22.149          | 22.238  | 22.327 |

| E      | 0.3960            | 0.400   | 0.4040 | 10.058          | 10.16   | 10.262 |

| е      | -                 | 0.0315  | -      | -               | 0.80    | -      |

| HE     | 0.462             | 0.466   | 0.470  | 11.735          | 11.8365 | 11.938 |

| L      | 0.016             | 0.020   | 0.0235 | 0.406           | 0.50    | 0.597  |

| L1     | -                 | 0.033   | -      | -               | 0.84    | -      |

| S      | -                 | 0.035   | -      | -               | 0.88    | -      |

| у      | -                 | -       | 0.004  | -               | -       | 0.10   |

| θ      | 0°                | -       | 5°     | 0°              | -       | 5°     |

## Notes:

- 1. Dimension D&E do not include interlead flash.

- 2. Dimension B does not include dambar protrusion/intrusion.

- 3. Dimension S includes end flash.

- 4. Controlling dimension: mm