## Zero-Peaking™, Ultra-low Power, 3-Channel SD Video Buffer with LPF

#### **Feature**

- 3-SDTV Filter

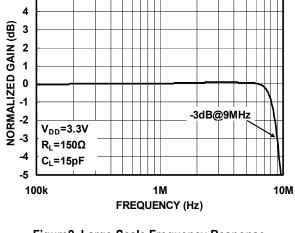

- 6th-order Butterworth Low-Pass Filter:

9MHz -3dB Bandwidth, 57.2dB Attenuation(27MHz)

- Support Multiple Input Biasing:

- Provide 80-mV Level-Shift when DC-Coupled

- Transparent Input Clamping when AC-Coupled

- Support External DC Biasing when AC-Coupled

- Low Quiescent Current: 3.85mA/CH (Typical)

- Slew Rate: 38V/µs

- 6dB Gain (2V/V) with Rail-to-Rail Output

- AC- or DC-Coupled Output Driving Dual Video Loads (75Ω)

- Wide Operation Range: +3.0V to +5.5V Single Supply

- Robust ESD Protection:

- HBM 8KV, CDM 2KV

- Lead-Free SOIC-8 Package Available

### **Applications**

- Video Signal Amplification

- Set-Top Box Video Driver

- PVR、DVD Player Video Buffer

- Video Buffer for Portable or USB-Powered Video Devices

- HDTV

#### Description

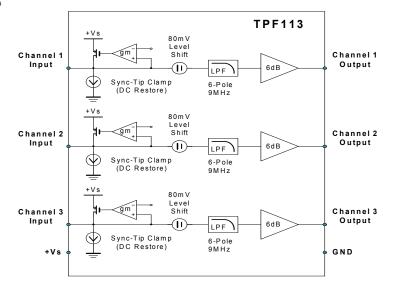

TPF113 is a 3-channel reconstruction video filter optimized for consumer video devices. With its video performance and low power consumption, it is choice for portable video applications. Integrated with 3 6th-order Butterworth filter, TPF113 can be used as a DAC reconstruction filter or ADC anti-aliasing filter. With its -3dB frequency of 9MHz, it is an choice for SD video applications including NTSC and PAL.

TPF113 accepts both AC- and DC-coupled inputs and its flexible biasing options meet the requirement of the most demanding applications. The integrated Transparent Sync-tip Clamp circuit restores DC voltage level of an AC-coupled Video signal. It translates the sync tip of a CVBS, Y', or RGB signal to a fixed 40mV. External biasing resistors can be used to restore signals without sync tip such as Pb' or Pr'. Integrated level shifter then raises the clamped video signal by 80mV, assuring passing through of video signal without being distorted. When the signal is DC-coupled, the level shifter will raise the signal by 80mV.

TPF113 may be used for different kinds of video buffering with 6dB gain(2V/V) and rail-to-rail output. It supports AC-and DC-coupling at the output.

TPF113 is designed to have exceptional ESD rating. It is a choice of protecting the main video processor chip from ESD or surge strikes in applications such as set-top-boxes.

TPF113 operates from a single supply with wide voltage range from +3.0V to +5.5V. Its very quiescent current of 3.85mA makes it an choice for battery-power or USB-power applications.

TPF113 is available in SOIC-8 package. Its operation temperature range is from -40°C to +85°C.

#### **Related Resources**

AN-1201: Application notes of TPF1xx

#### **Function Block**

#### **Order Information**

| Order Number | Operating<br>Temperature<br>Range | Package | Package<br>Options | Transport Media,<br>Quantity |

|--------------|-----------------------------------|---------|--------------------|------------------------------|

| TPF113-SR    | -40 to 85°C                       | SOIC-8  | MSL-3              | Tape and Reel, 4000          |

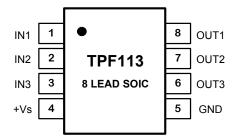

## **Configuration** (Top View)

| Pin<br>Number | Pin<br>Name | Function              |  |

|---------------|-------------|-----------------------|--|

| 1             | IN1         | First Input           |  |

| 2             | IN2         | Second input          |  |

| 3             | IN3         | Third input           |  |

| 4             | +Vs         | Positive power supply |  |

| 5             | GND         | Ground                |  |

| 6             | OUT3        | Third output          |  |

| 7             | OUT2        | Second output         |  |

| 8             | OUT1        | First output          |  |

## **Absolute Maximum Ratings**\*

|                                            | Parameters                                             | Value                                | Unit |  |

|--------------------------------------------|--------------------------------------------------------|--------------------------------------|------|--|

|                                            | Power Supply, V <sub>DD</sub> to GND                   | 6.0                                  | V    |  |

| PD                                         | Power dissipation , T <sub>A</sub> = 25°C, 8-Lead SOIC | 800 <sup>(1)</sup>                   | mW   |  |

| $V_{IN}$                                   | Input Voltage                                          | V <sub>DD</sub> + 0.3V to GND - 0.3V |      |  |

| I <sub>O</sub>                             | I <sub>O</sub> Output Current                          |                                      | mA   |  |

| $T_J$                                      | T <sub>J</sub> Maximum Junction Temperature            |                                      | °C   |  |

| T <sub>A</sub> Operating Temperature Range |                                                        | -45 to 85                            | °C   |  |

| T <sub>STG</sub>                           | T <sub>STG</sub> Storage Temperature Range             |                                      | °C   |  |

| TL                                         | Lead Temperature (Soldering, 10 sec)                   | 300                                  | °C   |  |

| $\theta_{JA}$                              | 8-Lead SOIC                                            | 130 <sup>(2)</sup>                   | °C/W |  |

- (1) This data was taken with the JEDEC low effective thermal conductivity test board.

- (2) This data was taken with the JEDEC standard multilayer test boards.

#### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                | Condition                  | Minimum<br>Level | Unit |

|--------|--------------------------|----------------------------|------------------|------|

| HBM    | Human Body Model ESD     | MIL-STD-883H Method 3015.8 | 8                | kV   |

| CDM    | Charged Device Model ESD | JEDEC-EIA/JESD22-C101E     | 2                | kV   |

<sup>\*</sup> **Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

# **Electrical Characteristics** All test condition is VDD = 3.3V, TA = +25°C, RL = 150 $\Omega$ to GND, unless otherwise noted.

| SYMBOL                  | PARAMETER                               | CONDITIONS                                                    | MIN  | TYP  | MAX   | UNITS |

|-------------------------|-----------------------------------------|---------------------------------------------------------------|------|------|-------|-------|

| Input Electric          | al Specifications                       |                                                               |      |      |       |       |

| $V_{DD}$                | Supply Voltage Range                    |                                                               | 3.0  |      | 5.5   | V     |

| ı                       | Out + (I \ (1)                          | V <sub>DD</sub> = 3.3V, V <sub>IN</sub> = 500mV, no load      |      | 11.6 | 14.3  | mA    |

| I <sub>DD</sub>         | Quiescent current (I <sub>Q</sub> ) (1) | V <sub>DD</sub> = 5.0V, V <sub>IN</sub> = 500mV, no load      |      | 14.7 | 18.4  | mA    |

| I <sub>CLAMP-DOWN</sub> | Clamp Charge Current                    | V <sub>IN</sub> =300mV, measure current                       | 1.5  | 2.0  | 5.1   | μA    |

| I <sub>CLAMP-UP</sub>   | Clamp Discharge Current                 | V <sub>Y</sub> = -0.2V                                        | -1.5 | -1.7 |       | mA    |

| V <sub>CLAMP</sub>      | Input Voltage Clamp                     | I <sub>Y</sub> = -100μA                                       | -40  | 0    | +40   | mV    |

| R <sub>IN</sub>         | Input Impedance                         | 0.5V < V <sub>Y</sub> < 1V                                    | 0.5  | 3    |       | МΩ    |

| AV                      | Voltage Gain (1)                        | $V_{IN}$ =0.5V,1V or 2V $R_L$ =150 $\Omega$ to GND            | 5.9  | 6.01 | 6.025 | dB    |

| ΔΑV                     | Channel Mismatch                        |                                                               | -2   |      | +2    | %     |

| V <sub>OLS</sub>        | Output Level Shift Voltage              | V <sub>IN</sub> = 0V, no load, input referred                 | 53   | 80   | 124   | mV    |

| V <sub>OL</sub>         | Output Voltage Low Swing                | $V_{IN}$ = -0.3V, $R_L$ =75 $\Omega$                          |      | 0.05 |       | V     |

| V <sub>OH</sub>         | Output Voltage High Swing               | $V_{IN}$ = 3V, $R_L$ =75 $\Omega$ to GND (dual load)          |      | 3.18 |       | V     |

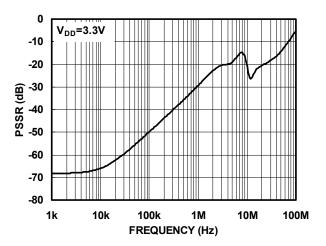

| PSRR                    | Power Supply Rejection Ratio            | $\Delta V_{DD}$ = 3.3V to 3.6V                                |      | 61   |       | dB    |

| rokk                    |                                         | $\Delta V_{DD} = 5.0 \text{V to } 5.5 \text{V}, 50 \text{Hz}$ |      | 67   |       | dB    |

| 1                       | Obs. Laine it a seed                    | $V_{IN}$ = 2V, 10 $\Omega$ , output to GND                    | 65   |      |       | mA    |

| Isc                     | Short-circuit current                   | $V_{IN}$ =0.1V, output short to $V_{DD}$                      | 65   |      |       | mA    |

| AC Electrical           | Specifications                          |                                                               |      |      |       | •     |

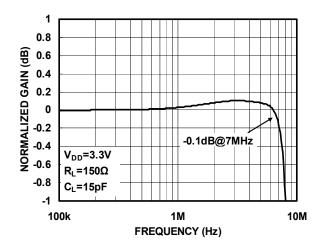

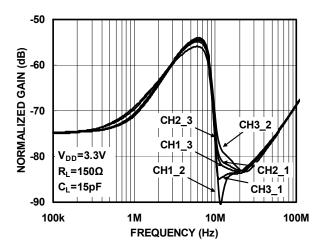

| f <sub>-1dB</sub>       | -1dB Bandwidth                          | R <sub>L</sub> =150Ω                                          | 7.6  | 8.2  | 9.1   | MHz   |

| f <sub>-3dB</sub>       | -3dB Bandwidth                          | R <sub>L</sub> =150Ω                                          | 7.8  | 9    | 10.5  | MHz   |

| Att <sub>27MHz</sub>    | Stop Band Attenuation                   | f = 27MHz                                                     | 38.2 | 57.2 |       | dB    |

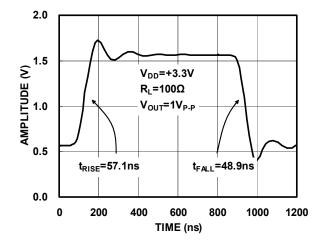

| SR                      | Slew Rate                               | 2V output step, 80% to 20%                                    |      | 38   |       | V/µs  |

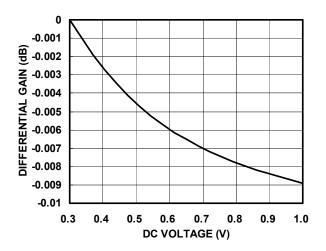

| dG                      | Differential Gain                       | Video input range 1V                                          | -0.1 | 0.4  | 0.8   | %     |

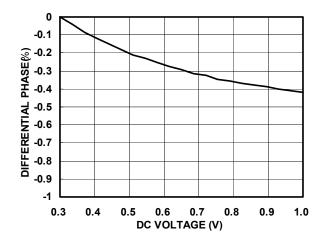

| dP                      | Differential Phase                      | Video input range 1V                                          | -1.1 | 0.7  | 1.1   | 0     |

| THD                     | Output Distortion(All Channel)          | f=1MHz, V <sub>OUT</sub> =1.4V <sub>PP</sub>                  | 0.03 | 0.1  | 0.2   | %     |

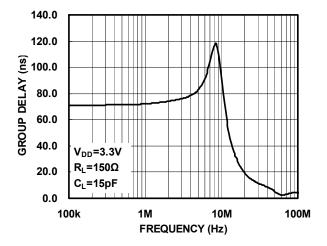

| D/DT                    | Group Delay Variation                   | f = 100kHz, 5MHz                                              |      | 5.4  |       | Ns    |

| t <sub>PD</sub>         | Propagation Delay                       | Maximum delay from input to output: 100kHz to 4.43MHz         |      | 80   | 127   | Ns    |

| $X_{TALK}$              | Channel Crosstalk                       | $f = 1MHz, V_{OUT}=1.4V_{PP}$                                 | -68  | -74  |       | dB    |

| SNR                     | Signal-to-Noise Ration                  | f= 100kHz to 4.43MHz                                          | 65   | 69   |       | dB    |

| SYMBOL                  | PARAMETER                               | CONDITIONS                                                    | MIN  | TYP  | MAX   | UNITS |

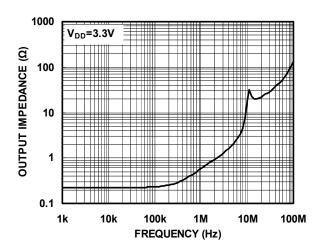

| R <sub>OUT_AC</sub>     | Output Impedance                        | f = 4.2MHz                                                    |      | 1.5  |       | Ω     |

| CLG                     | Chroma-Luma-Gain                        | 400kHz to 3.58MHz and 4.43MHz                                 |      | 0.18 | 0.4   | dB    |

| CLD                     | Chroma-Luma-Delay                       | 400kHz to 3.58MHz and 4.43MHz                                 |      | 5    |       | ns    |

Note: (1). 100% tested at T<sub>A</sub>=25°C.

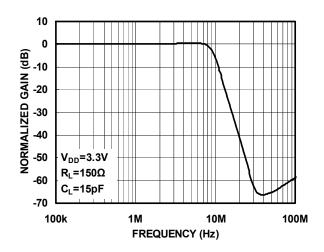

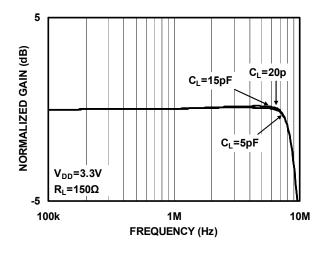

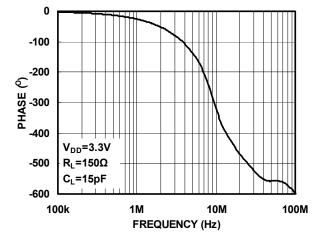

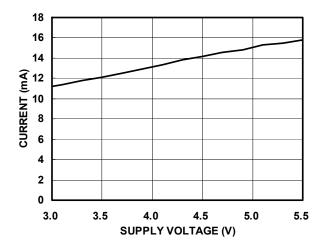

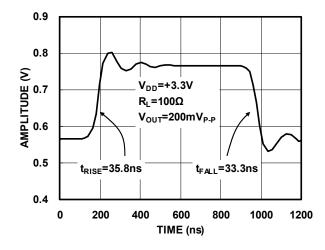

**Typical Performance Characteristics** All test condition is VDD = 3.3V, TA =  $+25^{\circ}$ C, RL =  $150\Omega$  to GND, unless otherwise noted.

5

Figure 1. Small-Scale Frequency Response

Figure 2. Large-Scale Frequency Response

Figure 3. Gain Vs. Frequency

Figure 4. Gain Vs. Frequency With CLOAD

Figure 5. Phase Vs. Frequency

Figure 6. Group Delay vs Frequency

Figure 7. PSRR Vs. Frequency

Figure 9. Crosstalk Vs. Frequency

Figure 11. Large-Signal Pulse Response Vs. Time

Figure8. Output Impedance Vs. Frequency

Figure 10. Current Vs. Supply Voltage

Figure 12. Small-Signal Pulse Response Vs. Time

Figure 13. Differential Gain (dG)

Figure 14. Differential Phase (dP)

### **Application Information**

The TPF113 is a single supply 3 channel rail-to-rail output amplifier achieving a -3dB bandwidth of around 9MHz and slew rate of about 38V/µs while demanding only 3.85mA(per channel) of supply current. This part is ideally suited for applications with specific micro power consumption and high bandwidth demands. As the performance characteristics above and the features described below, the TPF113 is designed to be very attractive for portable composite video applications.

### **Internal Sync Clamp**

The typical embedded video DAC operates from a ground referenced single supply. This becomes an issue because the lower level of the sync pulse output may be at a 0V reference level to some positive level. The problem is presenting a 0V input to most single supply driven amplifiers will saturate the output stage of the amplifier resulting in a clipped sync tip and degrading the video image. A larger positive reference may offset the input above its positive range.

The TPF113 features an internal sync clamp and offset function to level shift the entire video signal to the best level before it reaches the input of the amplifier stage. These features are also helpful to avoid saturation of the output stage of the amplifier by setting the signal closer to the best voltage range.

The simplified block diagram of the TPF113 in Page-1. The AC coupled video sync signal is pulled negative by a current source at the input of the comparator amplifier. When the sync tip goes below the comparator threshold the output comparator is driven negative, The PMOS device turns on clamping sync tip to near ground level. The network triggers on the sync tip of video signal.

# **Droop Voltage and DC Restoration**

Selection of the input AC-coupling capacitance is based on the system requirements. A typical sync tip width of a 64µs NTSC line is 4µs during which clamp circuit restores its DC level. In the remaining 60µs period, the voltage droops because of a small constant 2.0µA sinking current. If the AC-coupling

capacitance is 0.1µF, the maximum droop voltage is about 1mV which is restored by the clamp circuit. The maximum pull-up current of the clamp circuit is 1.7mA. For a 4µs sync tip width and 0.1µF capacitor, the maximum restoration voltage is about 80mV.

The line droop voltage will increase if a smaller AC-coupling capacitance is used. For the same reason, if larger capacitance is used the line droop voltage will decrease. Table 1 is droop voltage and maximum restoration voltage of the clamp for typical capacitance.

Table 1. Maximum restoration voltage and droop voltage of Y and CVBS signals for different capacitance

| CAP VALUE<br>(nF) | DROOP IN 60µs<br>(mV) | CHARGE IN 4µs<br>(mV) |  |  |

|-------------------|-----------------------|-----------------------|--|--|

| 100               | 1.2                   | 68                    |  |  |

| 1,000             | 0.12                  | 6.8                   |  |  |

### Low Pass Filter--Sallen Key

The Sallen Key is a classic low pass configuration. This provides a very stable low pass function, and in the case of the TPF113, a six-pole roll-off at around 9MHz. The six-pole function is accomplished with an RC low pass network placed in series with and before the Sallen Key.

### **Output Couple**

TPF113 output could support both "AC Couple" and "DC Couple", if use "AC Couple", this capacitor is typically between 220-µF and 1000-µF, although 470-µF is common. This value of this capacitor must be this large to minimize the line tilt (droop) and/or field tilt associated with ac-coupling as described previously in this document.

The TPF113 internal sync clamp makes it possible to DC couple the output to a video load, eliminating the need for any AC coupling capacitors, thereby saving board space and additional expense for capacitors. This makes the TPF113 extremely attractive for portable video applications. Additionally, this solution completely eliminates the issue of field tilt in the lower frequency. The trade off is greater demand of supply current. Typical load current for AC coupled is around 1mA, compared to typical 6.6mA used when DC coupling.

Output Drive Capability and Power Dissipation

With the high output drive capability of the TPF113, it is possible to exceed the +125°C absolute maximum junction temperature under certain load current conditions. Therefore, it is important to calculate the maximum junction temperature for an application to determine if load conditions or package types need to be modified to assure operation of the amplifier in a safe operating area. The maximum power dissipation allowed in a package is determined according to Equation:

$$PD_{\text{MAX}} = \frac{T_{\text{JMAX}} - T_{\text{AMAX}}}{\theta_{\text{JA}}}$$

Where:

$T_{JMAX}$  = Maximum junction temperature

T<sub>AMAX</sub> = Maximum ambient temperature

$\Theta$  JA = Thermal resistance of the package

The maximum power dissipation actually produced by an IC is the total quiescent supply current times the total power supply voltage, plus the power in the IC due to the load, or: for sourcing:

$$PD_{MAX} = V_{s} \times I_{SMAX} + (V_{s} - V_{OUT}) \times \frac{V_{OUT}}{R_{t}}$$

Where:

$V_S$  = Supply voltage

I<sub>SMAX</sub> = Maximum quiescent supply current

V<sub>OUT</sub> = Maximum output voltage of the application

R<sub>LOAD</sub> = Load resistance tied to ground

By setting the two PDMAX equations equal to each other, we can solve the output current and RLOAD to avoid the device overheat.

# Power Supply Bypassing Printed Circuit Board Layout

As with any modern operational amplifier, a good printed circuit board layout is necessary for optimum performance. Lead lengths should be as short as possible. The power supply pin must be well bypassed to reduce the risk of oscillation. For normal single supply operation, a single 4.7 $\mu$ F tantalum capacitor in parallel with a 0.1 $\mu$ F ceramic capacitor from VS+ to GND will suffice.

#### VIDEO FILTER DRIVER SELECTION GUIDE

| P/N      | Product Description                                 | Channel | -3dB Bandwidth | Package  |

|----------|-----------------------------------------------------|---------|----------------|----------|

| TPF110   | Low power, enable function and                      | 1-SD    | 9MHz           | SC70-5   |

| /TPF110L | SAG correction, 1 channel 6 <sup>th</sup> order     |         |                | SOT23-6  |

| TDE 440  | 9MHz                                                | 0.00    |                |          |

| TPF113   | Low power 3 channel, 6th-order 9MHz SD video filter | 3-SD    | 9MHz           | SO-8     |

| TPF114   | Low power 4 channel, 6th-order                      | 4-SD    | 9MHz           | MSOP-10  |

|          | 9MHz SD video filter                                |         |                | TSSOP-14 |

| TPF116   | Low power 4 channel, 6th-order                      | 6-SD    | 9MHz           | TSSOP-14 |

|          | 9MHz SD video filter for CVBS,                      |         |                |          |

|          | SVIDEO                                              |         |                |          |

| TPF123   | 3 channel 6th-order 13.5MHz,                        | 3-ED    | 13.5MHz        | SO-8     |

|          | 960H/720H-CVBS video filter or                      |         |                |          |

|          | Y'Pb'Pr 480P/576P video filter                      |         |                |          |

| TPF133   | Low power 3 channel, 6th-order                      | 3-HD    | 36MHz          | SO-8     |

|          | 36MHz HD video filter                               |         |                |          |

| TPF134   | Low power 3 channel, 6th-order                      | 1-SD&   | 9MHz           | MSOP-10  |

|          | 36MHz HD video filter and 1 channel                 | 3-SD    | 36MHz          | TSSOP-14 |

|          | SD video filter                                     |         |                |          |

| TPF136   | Low power 3 channel, 6th-order                      | 3-SD&   | 9MHz           | TSSOP-20 |

|          | 36MHz HD video filter and 3 channel                 | 3-HD    | 36MHz          |          |

|          | SD video filter                                     |         |                |          |

TPF113 Zero-Peaking, Ultra-low Power, 3-Channel SD Video Buffer with LPF

| TPF143 | Low power 3 channel, 6th-order 72MHz Full HD video filter | 3-FHD | 72MHz  | SO-8     |

|--------|-----------------------------------------------------------|-------|--------|----------|

| TPF144 | Low power 3 channel, 6th-order                            | 1-SD& | 9MHz   | MSOP-10  |

|        | 72MHz Full HD video filter and 1                          | 3-FHD | 72MHz  | TSSOP-14 |

|        | channel SD video filter                                   |       |        |          |

| TPF146 | Low power 3 channel, 6th-order                            | 3-SD& | 9MHz   | TSSOP-20 |

|        | 72MHz Full HD video filter and3                           | 3-FHD | 72MHz  |          |

|        | channel SD video filter                                   |       |        |          |

| TPF153 | Low power 3 channel, 6th-order                            | 3-CH  | 220MHz | SO-8     |

|        | 220MHz Full HD video filter                               |       |        |          |

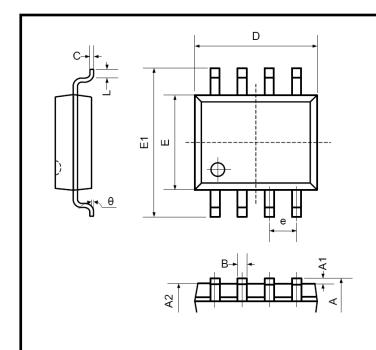

# **Package Outline Dimensions**

SOIC-8

| Dimensions |                |       | Dimensions In |       |  |

|------------|----------------|-------|---------------|-------|--|

| Symbol     | In Millimeters |       | Inches        |       |  |

|            | Min            | Max   | Min           | Max   |  |

| Α          | 1.350          | 1.750 | 0.053         | 0.069 |  |

| A1         | 0.100          | 0.250 | 0.004         | 0.010 |  |

| A2         | 1.350          | 1.550 | 0.053         | 0.061 |  |

| В          | 0.330          | 0.510 | 0.013         | 0.020 |  |

| С          | 0.190          | 0.250 | 0.007         | 0.010 |  |

| D          | 4.780          | 5.000 | 0.188         | 0.197 |  |

| Е          | 3.800          | 4.000 | 0.150         | 0.157 |  |

| E1         | 5.800          | 6.300 | 0.228         | 0.248 |  |

| е          | 1.270TYP       |       | 0.050TYP      |       |  |

| L1         | 0.400          | 1.270 | 0.016         | 0.050 |  |

| θ          | 0°             | 8°    | 0°            | 8°    |  |

#### IMPORTANT NOTICE

"PRELIMINARY" PRODUCT INFORMATION DESCRIBES PRODUCTS THAT ARE IN PRODUCTION, BUT FOR WHICH FULL CHARACTERIZATION DATA IS NOT YET AVAILABLE.

3PEAKIC MICROELECTRONICS CO. LTD BELIEVES THAT THE INFORMATION CONTAINED IN THIS DOCUMENT IS ACCURATE AND RELIABLE. HOWEVER, THE INFORMATION IS SUBJECT TO CHANGE WITHOUT NOTICE AND IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND (EXPRESS OR IMPLIED). CUSTOMERS ARE ADVISED TO OBTAIN THE LATEST VERSION OF RELEVANT INFORMATION TO VERIFY, BEFORE PLACING ORDERS, THAT INFORMATION BEING RELIED ON IS CURRENT AND COMPLETE. ALL PRODUCTS ARE SOLD SUBJECT TO THE TERMS AND CONDITIONS OF SALE SUPPLIED AT THE TIME OF ORDER ACKNOWLEDGMENT, INCLUDING THOSE PERTAINING TO WARRANTY, INDEMNIFICATION, AND LIMITATION OF LIABILITY. NO RESPONSIBILITY IS ASSUMED BY 3PEAKIC MICROELECTRONICS CO. LTD FOR THE USE OF THIS INFORMATION, INCLUDING USE OF THIS INFORMATION AS THE BASIS FOR MANUFACTURE OR SALE OF ANY ITEMS, OR FOR INFRINGEMENT OF PATENTS OR OTHER RIGHTS OF THIRD PARTIES. THIS DOCUMENT IS THE PROPERTY OF 3PEAKIC MICROELECTRONICS CO. LTD AND BY FURNISHING THIS INFORMATION, 3PEAKIC MICROELECTRONICS CO. LTD GRANTS NO LICENSE, EXPRESS OR IMPLIED UNDER ANY PATENTS, MASK WORK RIGHTS, COPYRIGHTS, TRADEMARKS, TRADE SECRETS OR OTHER INTELLECTUAL PROPERTY RIGHTS. 3PEAKIC MICROELECTRONICS CO. LTD OWNS THE COPYRIGHTS ASSOCIATED WITH THE INFORMATION CONTAINED HEREIN AND GIVES CONSENT FOR COPIES TO BE MADE OF THE INFORMATION ONLY FOR USE WITHIN YOUR ORGANIZATION WITH RESPECT TO 3PEAKIC MICROELECTRONICS CO. LTD INTEGRATED CIRCUITS OR OTHER PRODUCTS OF 3PEAKIC MICROELECTRONICS CO. LTD. THIS CONSENT DOES NOT EXTEND TO OTHER COPYING SUCH AS COPYING FOR GENERAL DISTRIBUTION, ADVERTISING OR PROMOTIONAL PURPOSES, OR FOR CREATING ANY WORK FOR RESALE.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). 3PEAKIC MICROELECTRONICS CO. LTD PRODUCTS ARE NOT DESIGNED, AUTHORIZED OR WARRANTED FOR USE IN AIRCRAFT SYSTEMS, MILITARY APPLICATIONS, PRODUCTS SURGICALLY IMPLANTED INTO THE BODY, AUTOMOTIVE SAFETY OR SECURITY DEVICES, LIFE SUPPORT PRODUCTS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF 3PEAKIC MICROELECTRONICS CO. LTD PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK AND INCLUSION DISCLAIMS AND MAKES NO WARRANTY, EXPRESS, STATUTORY OR IMPLIED, INCLUDING THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR PARTICULAR PURPOSE, WITH REGARD TO ANY DISCLAIMS PRODUCT THAT IS USED IN SUCH A MANNER. IF THE CUSTOMER OR CUSTOMER'S CUSTOMER USES OR PERMITS THE USE OF 3PEAKIC MICROELECTRONICS CO. LTD PRODUCTS IN CRITICAL APPLICATIONS, CUSTOMER AGREES, BY SUCH USE, TO FULLY INDEMNIFY 3PEAKIC MICROELECTRONICS CO. LTD, ITS OFFICERS, DIRECTORS, EMPLOYEES, DISTRIBUTORS AND OTHER AGENTS FROM ANY AND ALL LIABILITY, INCLUDING ATTORNEYS' FEES AND COSTS, THAT MAY RESULT FROM OR ARISE IN CONNECTION WITH THESE USES.

THE LOGO DESIGNS OF 3PEAKIC MICROELECTRONICS CO. LTD ARE TRADEMARKS OF DESIGNS. ALL OTHER BRAND AND PRODUCT NAMES IN THIS DOCUMENT MAY BE TRADEMARKS OR SERVICE MARKS OF THEIR RESPECTIVE OWNERS.

#### **Contact information:**

USA: 635 W. Alma School Road, Suite102

Chandler, USA.

AZ 85234

Shanghai-China: Room 401-407 No.1278 Keyuan Road,

Zhangjiang High-tech Park, Pudong New District,

Shanghai, China Zip Code: 201203

Suzhou-China: Suite 304, Building B2, Creative Industrial Park,

No.328 Xinghu Street, Industrial Park, Suzhou, Jiangsu Province, China

Zip Code: 215123